ISPD 2019 Contest on Initial Detailed Routing

Because the contest already finish, innovus license is expired.

For academic research, Cadence provides academic innovus license for use.

You can apply for the license through the following webpage:

https://www.cadence.com/content/cadence-www/global/en_US/home/services/cadence-academic-network/university-software-program.htmlAnnouncementsback to top ▲

| 05/27/2019 | Final Solution Files for the top-5 teams are released. |

| 04/24/2019 | Presentation slide is released. |

| 04/24/2019 | Final scores is released. |

| 04/24/2019 | Final Evaluation program updated. |

| 03/17/2019 | Evaluation program is updated. |

| 03/12/2019 | Evaluation program is updated. |

| 02/27/2019 | Runtime limit in seconds are available on the benchmark table. |

| 02/27/2019 | Alpha version results are available. |

| 02/22/2019 | Evaluation program is updated to fix corner spacing on cut layer reporting issue. |

| 02/17/2019 | Evaluation program is updated to fix corner spacing reporting issue. |

| 02/12/2019 | Evaluation program is updated to handle non-sufficient metal violation. |

| 02/03/2019 | Released two more benchmarks (test4 and test9). |

| 01/17/2019 | Evaluation program is updated to fix the multi-cut via counting issues. |

| 01/11/2019 | Evaluation program is updated to fix the library linkage issues. |

| 12/15/2018 | Released the evaluation program. Please refer to the README file for instruction. |

| 12/01/2018 | Released 4 benchmarks (test1-3, 6). |

| 10/15/2018 | Released 4 sample benchmarks. |

| 10/15/2018 | Problem Introduction and Tutorial for the ISPD 2019 Contest |

| 09/23/2018 | Contest topic announced. |

| 12/10/2018 | Registration deadline. |

Abstractback to top ▲

The 2019 ISPD contest augments the 2018 ISPD initial detailed routing contest by adding more realistic design rule settings faced by physical design practitioners in the industry.

Detailed routing can be divided into two steps. First, an initial detailed routing step is used to generate a detailed routing solution while handling the major design rules. Then a detailed routing refinement is performed to fix the remaining design rule violations. This proposed contest focuses on the initial detailed routing step.

Assuming that a global routing result is already well optimized for certain metrics (e.g., timing), a detailed router needs to honor the global routing result as much as possible. In this way, the optimized metrics are kept meanwhile avoids design rule violations. For example, Fig. 1(a) shows a global routing result for a net with a source pin A and sink pins B, C, and D. Because the path from A to B is timing critical, a global router identifies a short path from A to B. However, the path passes a local wiring congestion region which is not seen by the global router. If the detailed router routes wires over that region as shown in Fig. 1 (b), it will have design rule violations. Fig. 1 (c) shows a routing result without short/spacing violations but it will have timing degradation for the path from A to B. On the other hand, Fig. 1 (d) shows a desired solution.

Fig. 1

To minimize the disturbance for net topology, initial detailed routing plays an important role. If the initial detailed routing result can meet the most common routing rules even it is not fully DRC clean, the later detailed routing refinement will have less chance to largely disturb the routing results.

Benchmarksback to top ▲

You can find the first released testcase for the contest, that is a sample benchmark, in the below link:

Instruction to Setup the Development Environment for the ISPD 2019 ContestA tutorial is also published in the same link.

| Benchmark | Version | #std | #block macros | #net | #pin | #Layer | Die size | Tech. node | Runtime limit (seconds) | Comments | >

| ispd19_sample | 1 | 22 | 0 | 11 | 0 | 9 | 0.017x0.01mm2 | 45nm | - | This sample testcase is used for the tutorial purpose. |

| ispd19_sample2 | 1 | 22 | 1 | 16 | 0 | 9 | 0.017x0.01mm2 | 45nm | - | This sample testcase has a block and nets connecting to the block. |

| ispd19_sample3 | 1 | 5 | 1 | 7 | 5 | 16 | 1.90x2.00mm2 | 45nm | - | This sample testcase has IO pins, large die size and more metal layers. |

| ispd19_sample4 | 2 | 67 | 0 | 22 | 0 | 9 | 0.195x0.195mm2 | 32nm | - | This sample testcase has special PG nets and all the rules considered in the contest. | >

| ispd19_test1 | 1 | 8879 | 0 | 3153 | 0 | 9 | 0.148x0.146mm2 | 32nm | 3600 | Single-core design with standard cell only. |

| ispd19_test2 | 1 | 72094 | 4 | 72410 | 1211 | 9 | 0.873x0.589mm2 | 32nm | 18000 | Complete single-core design with four memory blocks. |

| ispd19_test3 | 1 | 8283 | 4 | 8953 | 57 | 9 | 0.195x0.195mm2 | 32nm | 3600 | DTMF design with three memory blocks and one PLL block. |

| ispd19_test4 | 1 | 146442 | 7 | 151612 | 4802 | 5 | 1.604x1.554mm2 | 65nm | 7200 | ISPD'15 mgc_matrix_mult_b test case. [*] |

| ispd19_test5 | 1 | 28920 | 6 | 29416 | 360 | 5 | 0.906x0.906mm2 | 65nm | 7200 | ISPD'15 mgc_pci_bridge32_b test case. [*] |

| ispd19_test6 | 1 | 179881 | 16 | 179863 | 1211 | 9 | 1.358x1.325mm2 | 32nm | 25200 | Quad-core design with 16 memory blocks. |

| ispd19_test7 | 1 | 359746 | 16 | 358720 | 2216 | 9 | 1.581x1.517mm2 | 32nm | 43200 | Quad-core design with double the number of standard cells with 16 memory blocks. |

| ispd19_test8 | 1 | 539611 | 16 | 537577 | 3221 | 9 | 1.803x1.708mm2 | 32nm | 43200 | Quad-core design with triple the number of standard cells with 16 memory blocks. |

| ispd19_test9 | 1 | 899341 | 16 | 895253 | 3221 | 9 | 2.006x2.151mm2 | 32nm | 43200 | Quad-core design with quadruple the number of standard cells and with 16 memory blocks. |

| ispd19_test10 | 1 | 899404 | 16 | 895253 | 3221 | 9 | 2.006x2.151mm2 | 32nm | 43200 | Quad-core design with quadruple the number of standard cells, with 16 memory blocks, and some extra routing blockages. |

[*] Placement was created with an academic placer using the DATC RDF methodology:

Jinwook Jung, Iris Hui-Ru Jiang, Jianli Chen, Shih-Ting Lin, Yih-Lang Li, Victor N. Kravets, and Gi-Joon Nam. 2018. DATC RDF: an academic flow from logic synthesis to detailed routing. In Proceedings of the International Conference on Computer-Aided Design (ICCAD '18). ACM, New York, NY, USA, Article 37, 4 pages. RDF: https://github.com/jinwookjungs/datc_robust_design_flow

Update history:

- 04/24/2019 - Released 4 hidden testcases, ispd18_test5, ispd18_test7, ispd18_test8 and ispd18_test10.

- 02/03/2019 - Updated ispd19_test4 and ispd19_test9

- 12/01/2018 - Updated ispd19_test1-3,6

- 10/20/2018 - Updated ispd19_sample4

- 10/15/2018 - Released the sample benchmarks.

Evaluationback to top ▲

Downloads:

Evaluation kit (latest update: 4/22/2019 , version: 9)Evaluation metric and ranking method (latest update: 12/15/2018)

Evaluation kit includes:

README - instruction of running evaluation

ispd19eval.sh - evaluation script

ispd19eval.tcl - supporting script for Innovus for design rules and connectivity checking

ispd19eval - evaluation binary for guide and track obedience checking and score calculation

ispd19eval.w - weights information for score calculation

Evaluation Script (ispd19eval.sh)

The evaluation script manages the whole evaluation process. It performs the following tasks:

- Starts Innovus to perform design rule and connectivity checking.

- Generates design rule violation and connectivity reports.

- Starts evaluation program to perform guide and track obedience checking, read the Innovus reports, and calculate the final score.

- Generates the score table as output.

Usage:

./ispd19eval.sh -lef <input LEF> -guide <input guide> -idef <input DEF> -odef <solution DEF> [-keep]

-lef : the input LEF file

-guide : the input route guide file

-idef : the input DEF file

-odef : the routed DEF file

-keep : when it is specified, the intermediate files (logs, reports, scripts, etc.) will not be cleaned after evaluation.

Example:

./ispd19eval.sh -lef sample/ispd19_sample.input.lef -guide sample/ispd19_sample.input.guide -def sample/ispd19_sample.output.def

Evaluation Program (optional)

If you already have design rule and connectivity reports generated by Innovus. You could use the evaluation program directly without using the evaluation script.

Usage:

./ispd19eval -lef <input LEF> -def <solution DEF> -guide <input guide> -georpt <design rule violation report> -conrpt <connectivity report>

-lef : the input LEF file

-guide : the input route guide file

-def : the routed DEF file

-georpt : the design rule violation report generated by Innovus

-conrpt : the connectivity report generated by Innovus

Submissionback to top ▲

Alpha submission

Below table shows the best results so far for the released benchmarks.

| Benchmark | Score |

| ispd19_test1 | 2293656.37 |

| ispd19_test2 | 55286802.02 |

| ispd19_test3 | 4433257.21 |

| ispd19_test4 | 81639407.48 |

| ispd19_test6 | 105491779.7 |

| ispd19_test9 | No valid solution. |

Final Contest Resultback to top ▲

1st Place:

– Dr. CU

The Chinese University of Hong Kong

Gengjie Chen, Haocheng Li, Bentian Jiang, Jingsong Chen, Evangeline Young

2nd Place:

– NTUidRoute

National Taiwan University

Chen-Chia Chang, Chia-Ming Chang, Wei-Kai Liu, Chen-Hao Hsu, Yao-Wen Chang

3rd Place:

– Kim & Lee

POSTECH

Daeyeon Kim, Sung-Yun Lee, Minhyuk Kweon, Seokhyeong Kang

Fuzhou University and National Tsing Hua University

Zhen Zhuang, Chien-Hao Tsou, Weida Zhu, Chao-Yuan Huang, Genggeng Liu, Wenzhong Guo, Ting-Chi Wang

4th Place:

– None as we have two 3rd places.

5th Place:

- SmartDR

Universidade Federal de Pelotas

Stephano Gonçalves, Felipe Marques

Final Solution Filesback to top ▲

Below you can find the link to download the final solution for each benchmark from the top 5 teams.

Each benchmark has two directories:

def - with DEF solution files.rpt - with score reports from the contest.

File name starts with the team ID. Below are the team IDs followed by team names and position in the final ranking

1 - SmartDR (5th Place)7 - Kim & Lee (3rd Place)

10 - TripleZ (3rd Place)

12 - NTUidRoute (2nd Place)

15 - Dr. CU (1st Place)

Scheduleback to top ▲

| September 23, 2018 | Contest topic announced. |

| October 15, 2018 | Sample benchmark suite release. |

| December 01, 2018 | Benchmark suite release. |

| December 10, 2018 | Deadline for contest registration. |

| December 15, 2018 | Details about evaluation metrics and evaluator release. |

| February 12, 2019 | Deadline to receive alpha router executable submissions from all teams. |

| March 01, 2019 | Deadline to receive beta router executable submissions from all teams. |

| March 17, 2019 | Deadline to receive final router executable submissions from all teams at 2:00pm (PST). |

| April 14-17, 2019 | Contest results will be announced at the symposium. |

Registrationback to top ▲

Deadline: December 10, 2018.

For registration, please send a completed Registration Form to ispd2019contest@gmail.com

Contest Organizersback to top ▲

| Gracieli Posser | Cadence |

| Wen-Hao Liu | Cadence |

| Stefanus Mantik | Cadence |

| William Chow | Cadence |

| Yixiao Ding | Cadence |

| Amin Farshidi | Cadence |

FAQback to top ▲

Please refer to the 2018 ISPD Contest FAQ in the below link:Your question may be already answered there. If not, please contact us ispd2019contest@gmail.com.

-

Q: Can we assume that every net has a global routing guide?

A: Yes..

-

Q: Can guide have DRC violation?

A: Yes. Guide sometimes may have some DRC violation. You may need to violate the guide to resolve the violation.

-

Q: Can guide have off track via?

A: Yes. Off track via and wire can be expected in the guides. Some pins may be off track and need off track via and wire to access them.

-

Q: Is it OK to use patch metals to fix same-net min spacing violations?

A: Yes, you can.

-

Q: How patch metals influence in the score? They are included in the wire length penalty? If so, the length of a patch wire is its maximum x-y length?

A: The patch metals are not included in the wire length. However, you need to be aware that by adding patch metal to solve same-net spacing violation, you will eventually increase the effective metal width on that area. Thus, the required spacing from that patch to other metal will be larger which may introduce new diff-net spacing violations.

-

Q: In ISPD_2019_test3, there is a layer named OVERLAP, and there are several obstructions using this layer. Can we assume that we don't need to consider any of this information?

A: Yes. That’s the top-most layer and you’re not supposed to route on that layer anyway. So, any object on that layer can be ignored.

-

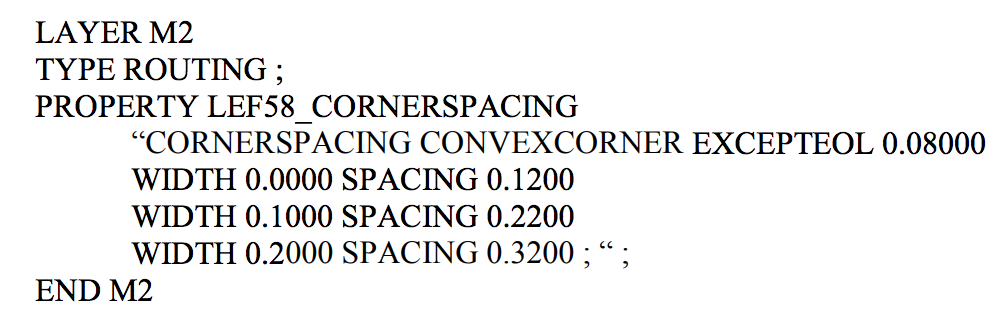

Q: A parallel-run spacing violation is observed in ispd18_test1 (shown in the following figure). We are confused why it is regarded as a parallel-run spacing violation. We are using the test case as well as the evaluator for ISPD'18 (not ISPD'19), so there is no considering for corner-to-corner violation. The description of this violation from Innovus is as follows.

======

Regular Via of Net net554 & Pin of Cell inst5025

Actual: 0.098 Min: 0.1 Type: ParallelRun

bbox = (126.335, 106.530) (126.375, 106.620)

======

What are the two parallel edges that causes this parallel-run violation? Should the two edges have positive parallel-run length (i.e., has some overlap either in X direction or in Y direction)?

A: In this case, the spacing is a corner-to-corner spacing with negative PRL (i.e., no projection overlap).

-

Q: The example of corner-to-corner in below figure, the spacing rule and 0.15 is used as the wire width. Is this 0.15 horizontal rectangle on the same layer or different layer?

A: In this example, all the wires are on the same layer. And in this contest, all the rules are applied to the metal on the same layer.

-

Q: Are all of Width1, Width2, and Width3 are considered in the parallel run spacing? If so, what are the corresponding parallel run lengths?

A: Assuming Width1, Width2, and Width3 belong to 3 different WIDTH range in the spacing table, the spacing will be checked based on the following:

- a) Width1 spacing: use PRL1 + PRL2 + PRL3 as the PRL for this width

- b) Width2 spacing: use PRL2 + PRL3 as the PRL for this width

- c) Width3 spacing: because the metal-height of this metal is less than the metal-width, the height value should be used as the “WIDTH” (let’s call it “effective-width”) to determine the spacing. Depending on the value for this effective-width, it may fall into either Width1 spacing or Width2 spacing (or even Width3 spacing if the effective-width still meet the threshold). The PRL for this spacing will be PRL3.

-

Q: Considering the figure from previous question, for Width3, PRL3 + PRL4 is used as effective-width and PRL3 is used as PRL, right?

A: Assuming that the picture is drawn to scale, then yes, effective-width is PRL3 + PRL4 while PRL is PRL3.

The general case:

If Width3 > PRL3 + PRL4 then

- Effective-width = PRL3 + PRL4

- PRL = PRL3

If Width3 < PRL3 + PRL4 then

- Effective-width = Width3

- PRL = PRL3

-

Q: Can we apply the ILP solver to our program in this contest? Is there any ILP solver library which we can directly use in the contest testing environment?

A: Yes, you can apply ILP solver. We are not providing any ILP solver library.

-

Q: If there is no edge in the PARALLELEDGE search window(line2), does the original EOL rule(line1) without PARALLELEDGE still exist??

A: Yes, the original EOL rule (line1) still exists if it is defined in the LEF.

If these lines are defined:

SPACING 0.08 ENDOFLINE 0.08 WITHIN 0.025 ;

SPACING 0.10 ENDOFLINE 0.08 WITHIN 0.025 PARALLELEDGE 0.10 WITHIN 0.025 ;

Then the followings are the EOL spacing required:

- a. If there is an edge on the parallel edge search window, then *BOTH* rules apply.

- So, the EOL spacing needs to be >= 0.10 *AND* >= 0.08 (which we can just take the max: >= 0.10).

- b. If no edge exist on the paralle edge search window, then *ONLY* the first rule (line1) applies.

- So, the EOL spacing needs to be >= 0.08.

-

Q: Can we apply the ILP solver to our program in this contest? Is there any ILP solver library which we can directly use in the contest testing environment?

A: Yes, you can apply ILP solver. We are not providing any ILP solver library.

-

Q: If a cut is partially in cutWithin, is it considered in the number of adjacent cuts? For example, in Fig. 3(b), if cut #2 overlaps with the cutWithin frontier, is there a violation?

A: If cut#2 is exactly cutWithin away from cut#0, then no, there is no violation.

If cut#2 is < cutWithin away from cut#0, then yes, there is violation.

-

Q: I see that the evaluation of ISPD2019 has two metrics about shorts:

- Short metal area / M2 pitch (500)

- Number of short violations (500)

While last year, ISPD2018 there is only one

- Short metal area / M2 pitch (500)

Does it mean that shorts will be considered twice this year? And what does M2 pitch mean?

A: a) Yes, one short violation will result in two costs in the table, number of shorts and area of shorts.

b) We use square of M2 pitch as one unit of area of shorts. M2 pitch means the distance between two tracks on M2, which is defined in DEF file. For example, if M2 pitch is 0.1um, 1 unit of area of shorts is 0.01 um^2. Therefore, 1 um^2 of short area is translated to 100 units and the cost will be 100 * 500 = 50000

At the same time, each short violation is translated to cost of 500.

For example, 10 short violations cost 10 * 500 = 5000

So, comparing many small area violations ( e.g., 100 x 0.01um^2 ) and one big area violation ( e.g. 1 x 1um^2 ) with equal total short area, many small area violation cost higher.

-

Q: Consider the case in the pictures in annex with the following spacing configuration:

SPACING 0.060000 ;

- SPACING 0.090000 ENDOFLINE 0.090000 WITHIN 0.025000 ;

- SPACINGTABLE

- PARALLELRUNLENGTH

- 0.000000

- WIDTH 0.000000 0.060000

- WIDTH 0.100000 0.100000

- WIDTH 0.750000 0.250000

- WIDTH 1.500000 0.450000 ;

The object on the left requires 0.1 horizontal spacing since it has more than 0.1 width (in both axis). What is the spacing criteria for the vertical axis? It seems that if the y distance is more than 0.7 there is no violation. What defines this value?

No violation:

With violation:

A: In corner-to-corner spacing region where PRL < 0 both in vertical and horizontal direction (i.e., no projection overlap), then the spacing should be taken from the first column of the corresponding spacing row and measure the distance in Euclidean fashion.

In the given example, the width of the left object is 0.1 < w <= 0.75, so the second row will be used, thus the spacing required is 0.10.

In the first picture, the horizontal distance is 0.08 (this is estimated since the ruler does not end exactly at the edge of the right metal)

while the vertical distance is 0.07. So, the actual spacing is: sqrt((0.08^2)+(0.07^2)) = 0.106 which is > 0.10, so spacing is OK.

In the second picture, the horizontal distance is 0.07 while the vertical distance is also 0.07.

The actual spacing is: sqrt ((0.07^2)+(0.07^2)) = 0.09899 which is < 0.10, so this is a spacing violation.

-

Q: From what I noticed a line in the spacing table is trigered only if the object meets the width in both axis. A 0.95 height and 0.2 width would require only 0.06 spacing in both axis. Is it right?

A: The WIDTH keyword in the SPACINGTABLE syntax refers to the “width” of the metal which is the smallest dimension of that metal.

This is not to be confused with the metal dimension itself which consist of width (i.e. horizontal span) and height (i.e. vertical span).

For the sake of clarity, let’s note the min-dimension “width” as W (upper case “w”), and metal width and height as ‘w’ and ‘h’ respectively (lower case).

If a metal with w = 0.2 and h = 0.095 dimension (a short but wide metal), the W = min(w,h) = min(0.2, 0.095) = 0.095. Thus first spacing row applies.

If a metal with w = 0.095 and h = 0.2 dimension (a tall and narrow metal), the W = min(w,h) = min(0.095, 0.2) = 0.095. Still the first spacing row applies.

Note, the spacing value is applied to all directions: horizontal, vertical, and corner (measured in Euclidean style).

-

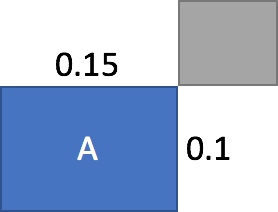

Q: If a cut is partially in cutWithin, is it considered in the number of adjacent cuts? For example, in Fig. 3(b), if cut #2 overlaps with the cutWithin frontier, is there a violation?In the corner-to-corner rule, if there is a rectangle like the following figure like the following and the rule specification is the same as the example.

In this case, both 0.15 and 0.1 is more than 0.08 so we need to consider corner-to-corner. And max(0.15, 0.1) = 0.15 so we should use spacing 0.22. Is this correct? However, if I increase 0.15 to a very large number, this becomes a horizontal wire with width 0.1, then it should use width 0.1 and spacing 0.12 according to the example. This contradicts with the 0.15*0.1 rectangle. Where is wrong? How should I consider the rectangle?

A: No. The WIDTH for 0.15x0.1 rectangle should be taken from the min(0.15, 0.1) which is 0.1. So, the spacing will be 0.120 (first row in the CORNERSPACING table).

-

Q: In the parallel condition of EOL rule, if the other parallel wire A has the bottom EOL edge in gray region of wire B, do we still consider EOL rule of B?

A: Yes, we still need to consider EOL rule for B. In this example (assuming that the top edge of B and the bottom edge of A are both EOL edges), A is considered the parallel-edge of wire B because it is in the grey region. Similarly (since A is also an EOL edge), B is considered the parallel-edge of wire A.

Contactback to top ▲

For registration or inquiry, please send emails to ispd2019contest@gmail.com.