# Physical Design Challenges and Innovations to Meet Power, Speed, and Area Scaling Trend

LC LU

TSMC

TSMC Fellow/Senior Director, R&D

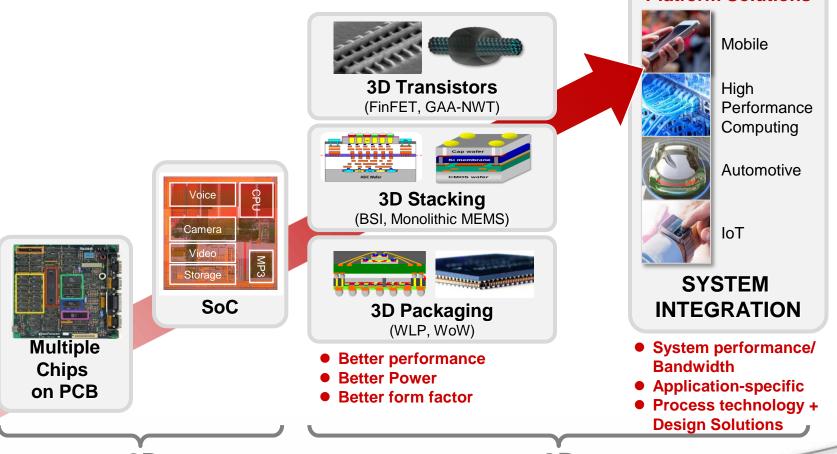

## **Chip and System Integration Trends for Better PPA & System Performance**

2D

3D

**Platform Solutions**

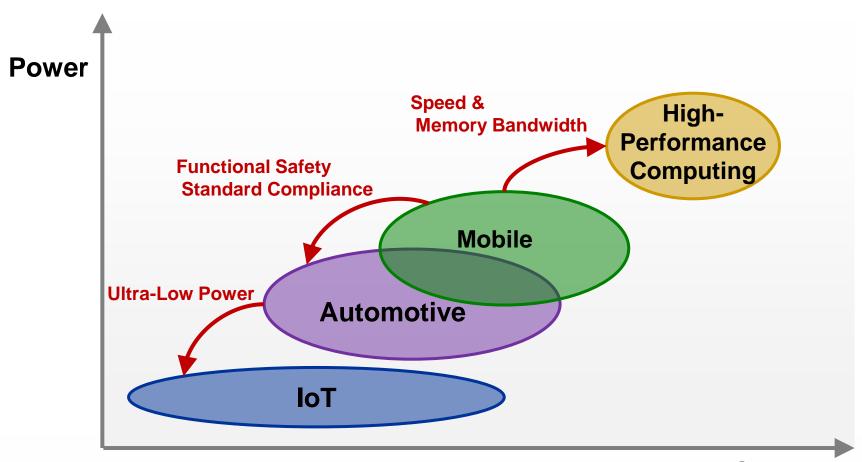

### Application-Optimized Design Platforms Area, Performance and Power

#### **Semiconductor Trend**

- Area: process primary dimension scaling slows down

- Very challenging to continue Moore's law economically

- Process and design co-optimization to provide enough area scaling

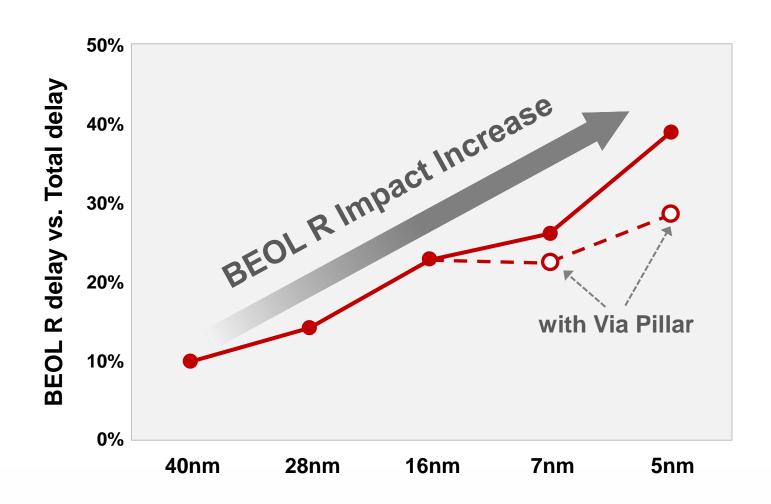

- Performance: dimension scaling grows metal and via resistance exponentially

- Fully automatic and smart via pillar design flow to reduce high resistance impact

- Power: ultra low voltage for ultra low power

- Robust design and variation modeling at low voltages

- Heterogeneous integration

- Low cost and high system performance 3D packaging

- High physical design complexity

- Machine learning to be applied to physical design

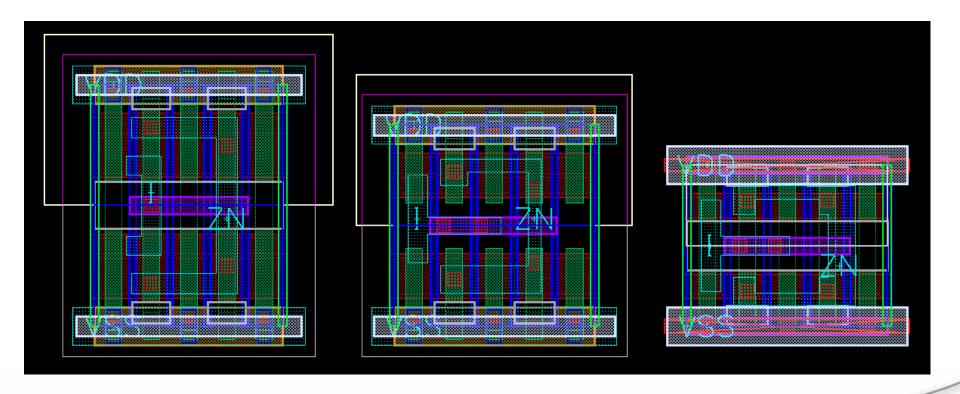

#### **Area Scaling**

- Process primary dimension (metal, gate and fin pitch) scales less and per generation cadence takes longer

- Process-design co-optimization innovation to keep area scaling

- Fin depopulation to increase cell density

- Power plan and cell layout co-optimization to increase cell placement utilization

- EUV to increase routing density

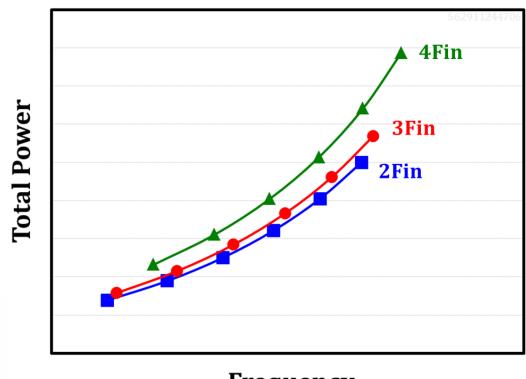

### Fin Depopulation can Increase Density and Reduce Process Dimension Scaling Pressure

4-fin cell

3-fin cell

2-fin cell

### Fin Depopulation can Increase Speed and Power Efficiency

- Higher fins have highest speed

- Fewer fins have highest speed@same power and lowest power@same speed

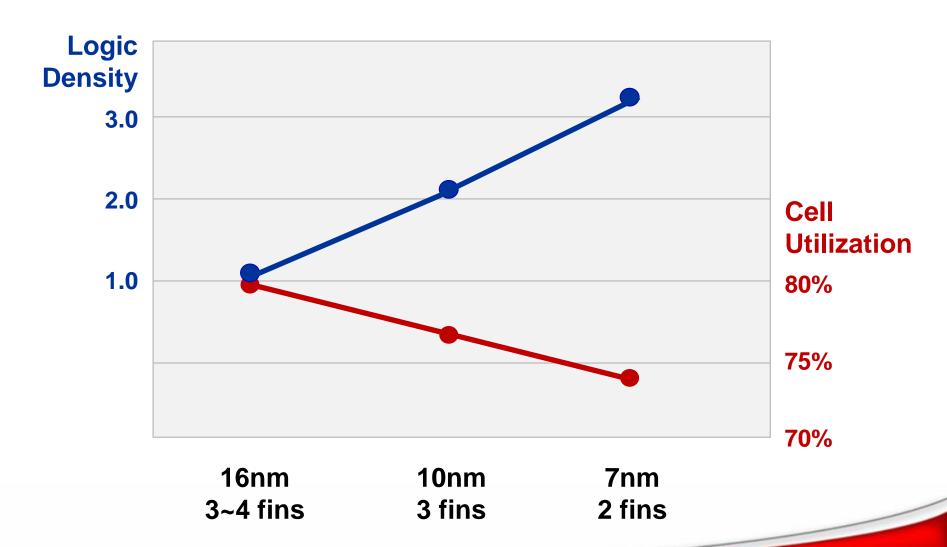

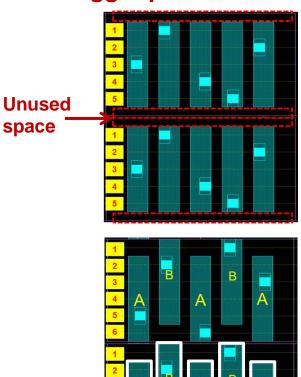

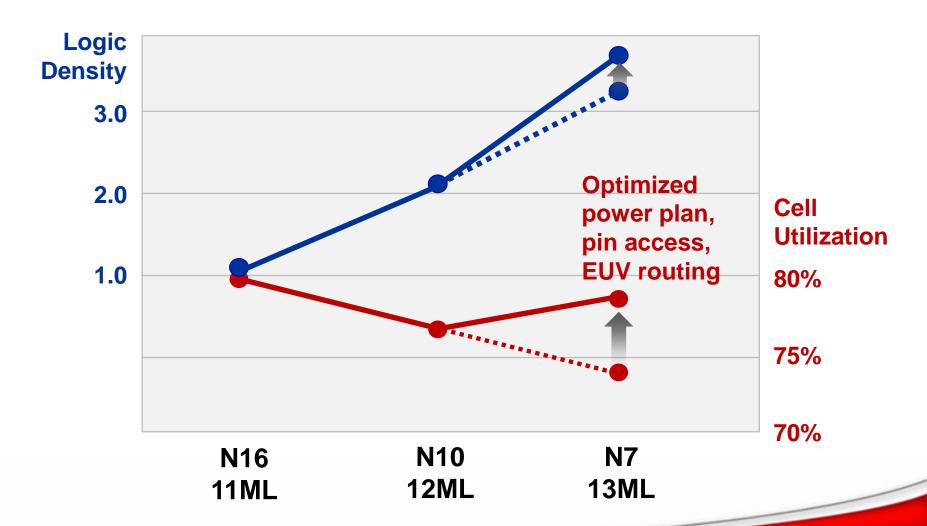

### Fin Depopulation Impact on Logic Density and Cell Utilization

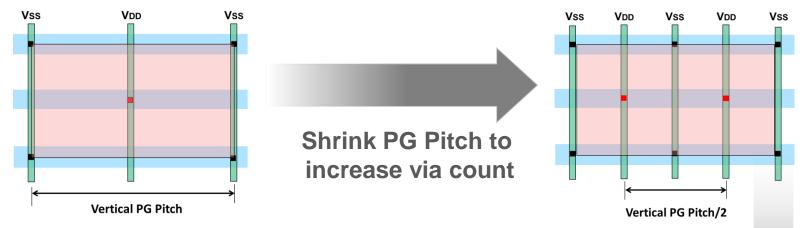

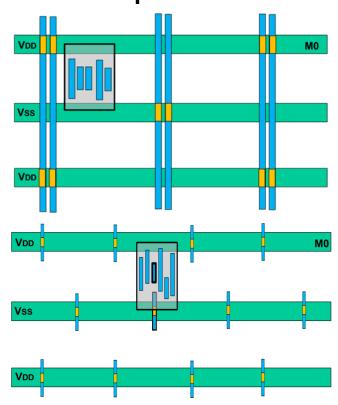

### Logic Density Improvement (I) Power Plan Optimization

To improve power plan IR, PG via count is increasing over technology generations

2x PG Density

However, shrinking PG pitch impacts routing resources.

So different and new PG design approaches evolved

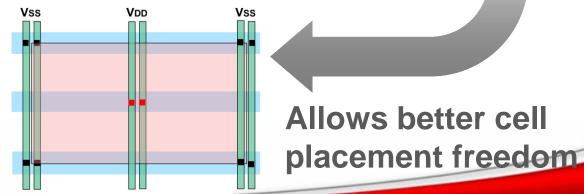

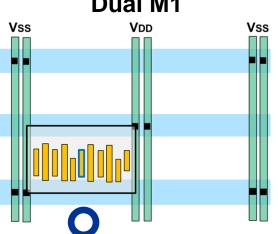

#### **Logic Density Improvement (II)** Power Plan and Cell Layout Co-optimization

PG design has to be friendly to cell architecture (Uniform → Dual)

Cell re-Design

Big cell design has to be redesigned to be compatible with **Dual PG architecture**

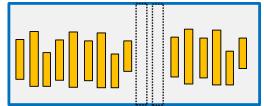

### Logic Density Improvement (III) Power Plan and Cell Layout Push to Limit

#### Power strap:

Less cells placed under PG

Power stub:

More cells placed under PG

No stagger pin: 5 access points

Stagger pin: 6 access points

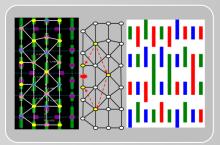

### Logic Density Improvement (IV) EUV to Increase Routing Density

Inverse Litho.

Multiple patterning

EUV

Directed Self-Assembly

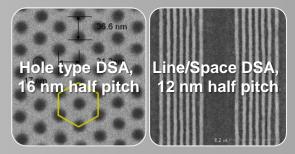

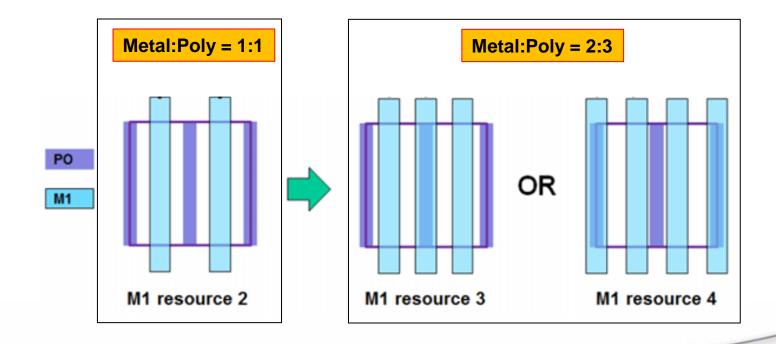

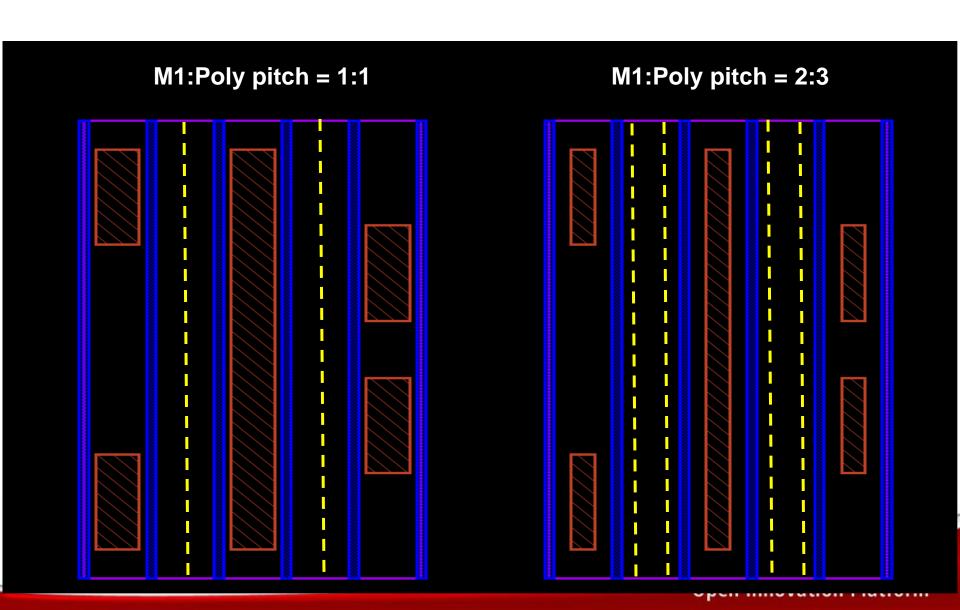

### EUV Metal Metal : Poly pitch = 2 : 3

- More Metal resources for logic density improvement

- 2 library sets are needed for two metal offset.

#### **Less Coupling from Metal : Poly = 2 : 3**

#### More Routing from Metal: Poly = 2:3

## **Enhanced Logic Density and Cell Utilization Trends**

### Performance Scaling

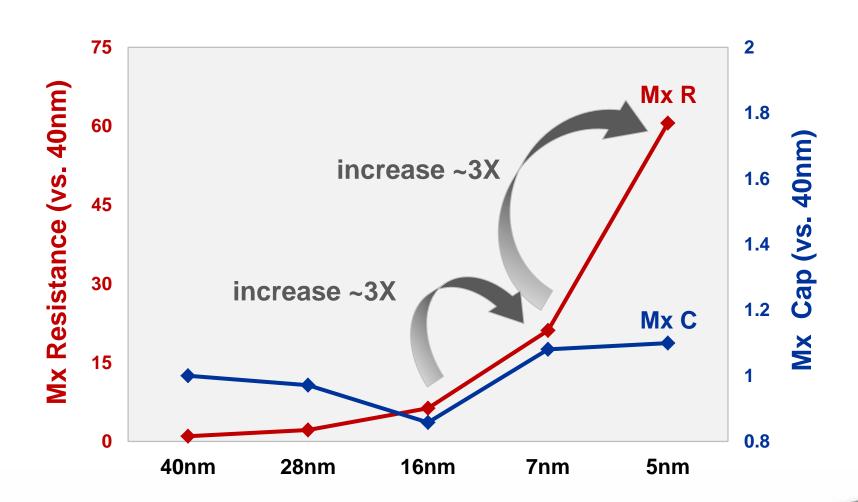

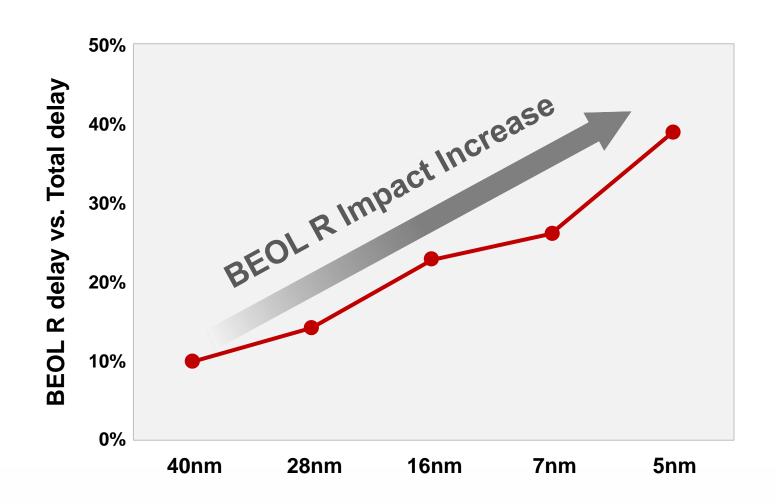

- Process dimension scaling grows metal and via resistance exponentially

- Fully automatic and smart EDA design flow is needed to effectively solve high resistance issue for 7nm and beyond

#### **Cross Node Metal RC Scaling**

### **Cross Node Wire R and Via Impact**

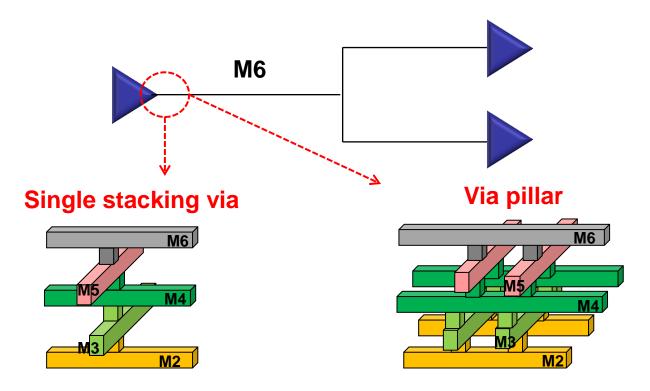

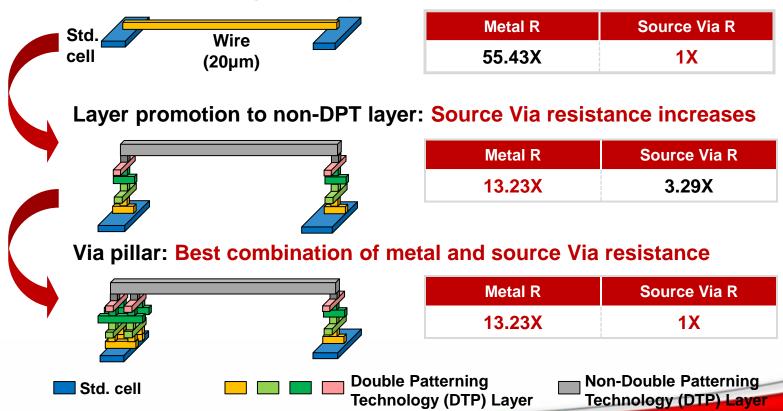

#### **VIA Pillar**

- Large drivers + upper thick metal + via pillar to reduce transistor, metal and via resistance

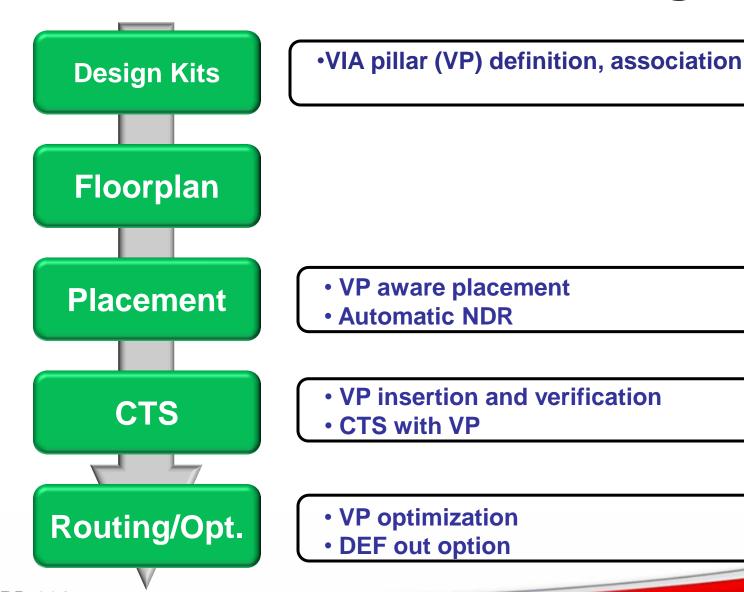

- VIA-Pillar enablement is complex and requires EDA enablement across all Implementation phases

#### Via Pillar Insertion

- Implies layer promotion for better wire resistance

- Effectively reduces source Via resistance

**Connection through DPT layer: DPT wire resistance dominates**

### **Cross Node Wire R and Via Impact**

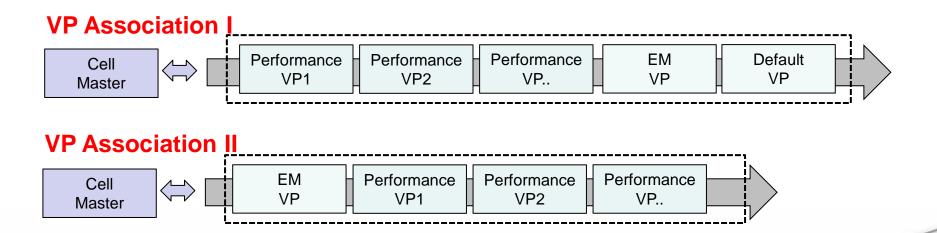

### Via Pillar Type and Usage

- EM via pillar (EM VP), used to guarantee cell-level EM, has to be 100% inserted

- One cell master will only have 1 EM VP

- Performance via pillar (Performance VP), which is larger than EM VP, can reduce more resistance

- One cell master can have multiple performance VP

#### Via Pillar Automatic Design Flow

### Voltage and Power Scaling

- Low voltage design reduces power effectively

- Low voltage design challenges

- Functionality robustness

- Accurate variation modeling

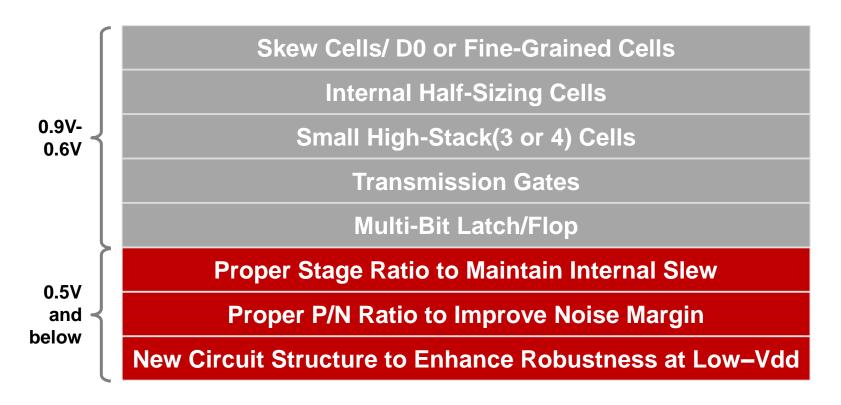

#### **Ultra-Low-Voltage Standard Cell Solution**

Improve cell performance by reducing delay degradation and variation induced by low-Vdd

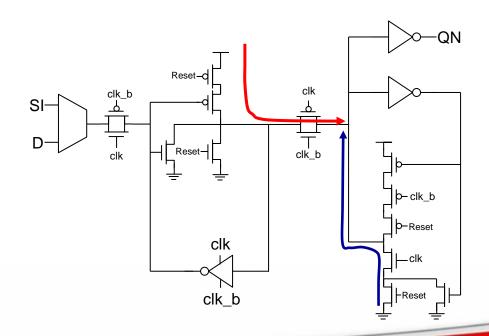

#### Flop Low Voltage Design Robustness

- High sigma design checks are required to ensure robust operation at low operating voltage

- For write operation, forward path (red) must be stronger than feedback path (blue)

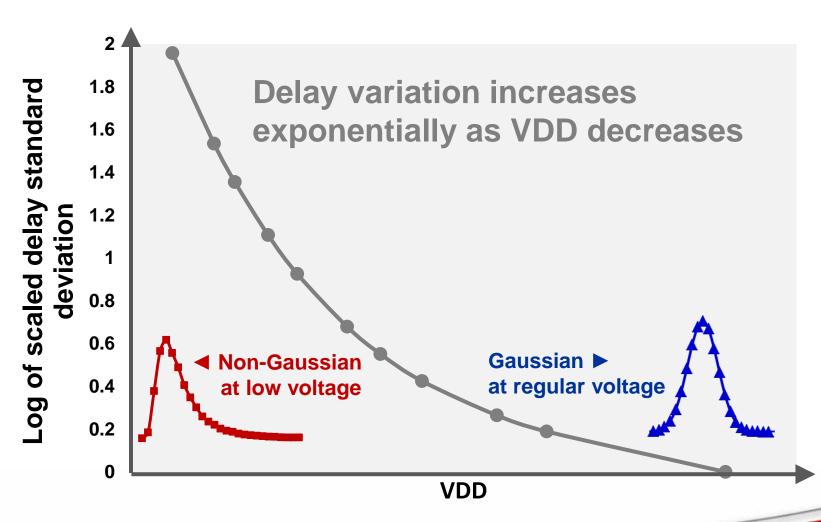

### Delay Variation Increases at Lower VDD

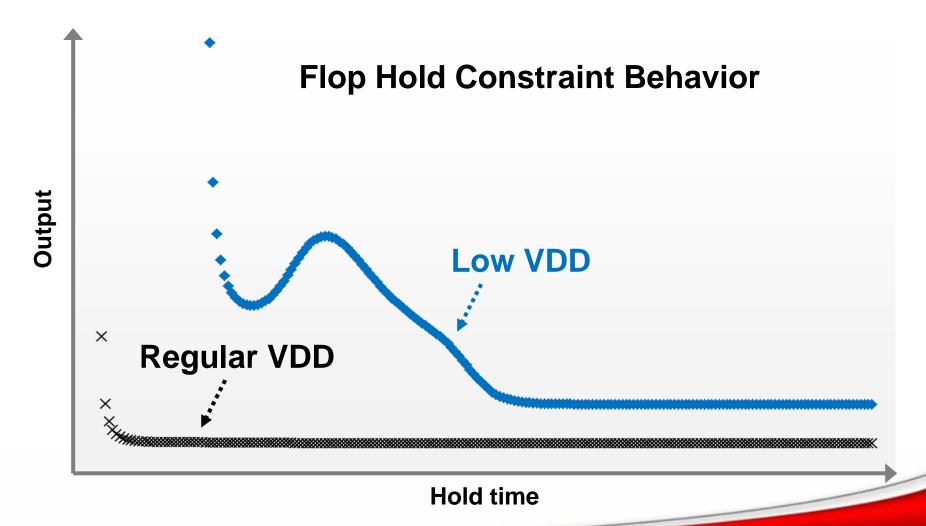

### Abnormal Hold-Time Caused by Low-Vdd Non-Gaussian Behavior

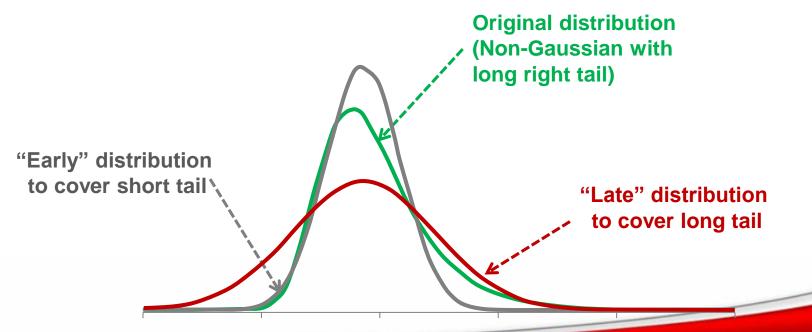

#### Solutions for Low-Vdd Variations (I)

- Methodology improvement

- Timing values are models by both "mean" and "early/late distribution"

- Implement the new models in timing characterization and STA tools

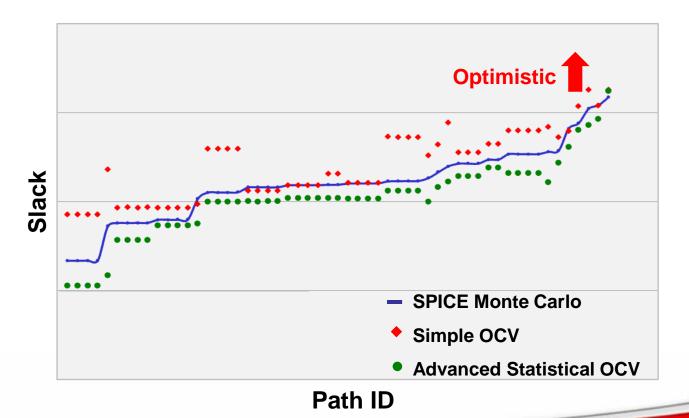

#### Solutions for Low-Vdd Variations (II)

By using new timing model and advanced statistical OCV method, we achieve more accurate STA results compared to Monte-Carlo simulations

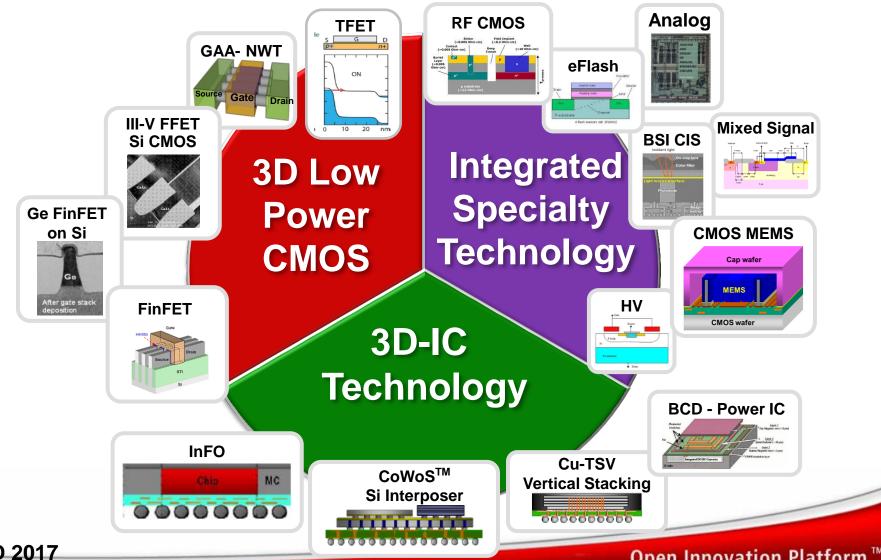

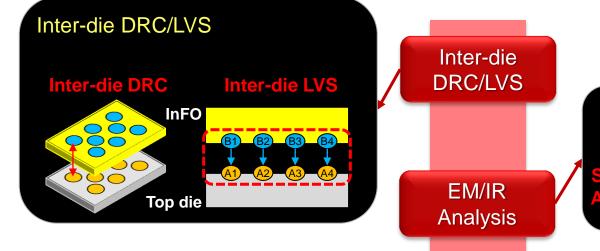

#### Heterogeneous Integration

- Low cost and high system performance

- InFO and CoWoS integration

- Integrated EDA design flow for package and chips

### **Future Device Possibilities Through Heterogeneous Technology Integration**

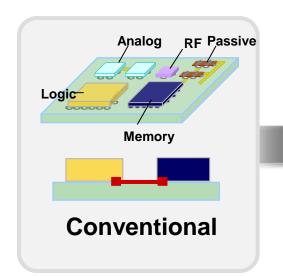

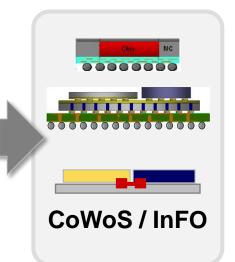

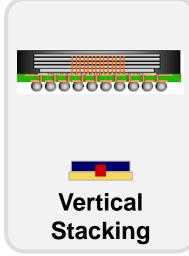

### 3D Packaging for Better System Performance and Form Factor

Conventional SIP or MCM (Wirebond, Flipchip, SMT)

3D Wafer-based System Integration

(CoWoS, InFo-PoP, Vertical Stacking, Wafer Bonding)

Sources: A-SSCC 2014, IEDM 2014, VLSI 2015

**ISPD 2017**

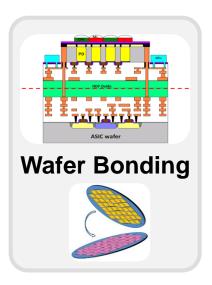

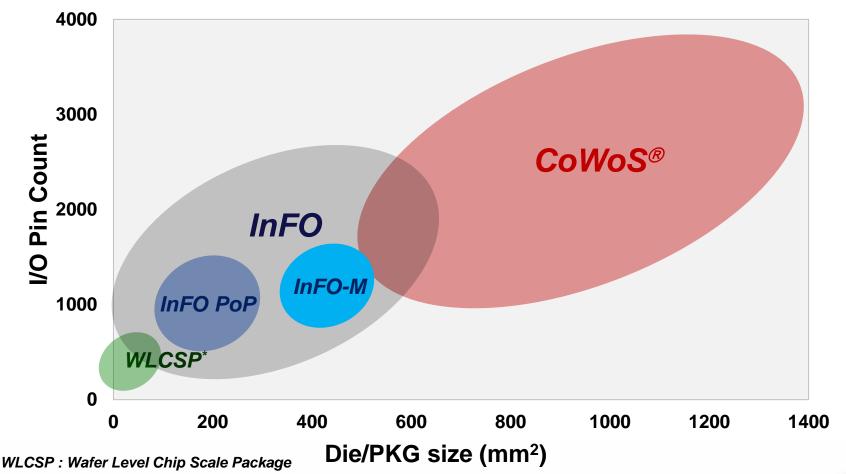

### Different Systems Require Different Packaging Solutions

\*\* InFO : Integrated Fan-Out

\*\*\* CoWoS : Chip on Wafer on Substrate

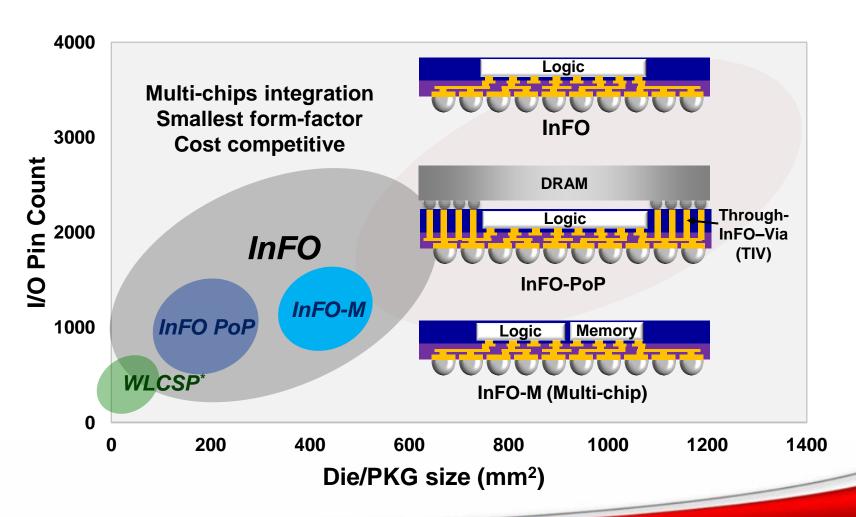

## Wafer-Level Packaging Technologies: Integrated Fan-Out (InFO)

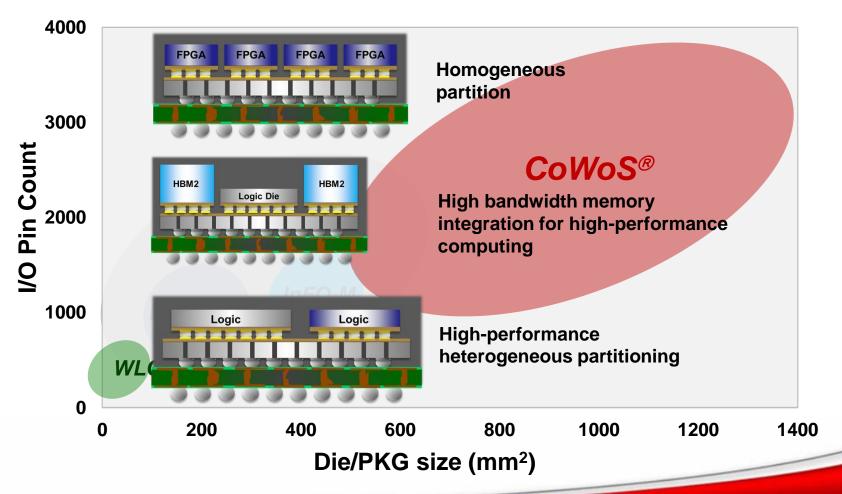

### Wafer-Level Packaging Technologies: Chip-on-Wafer-on-Substrate (CoWoS)

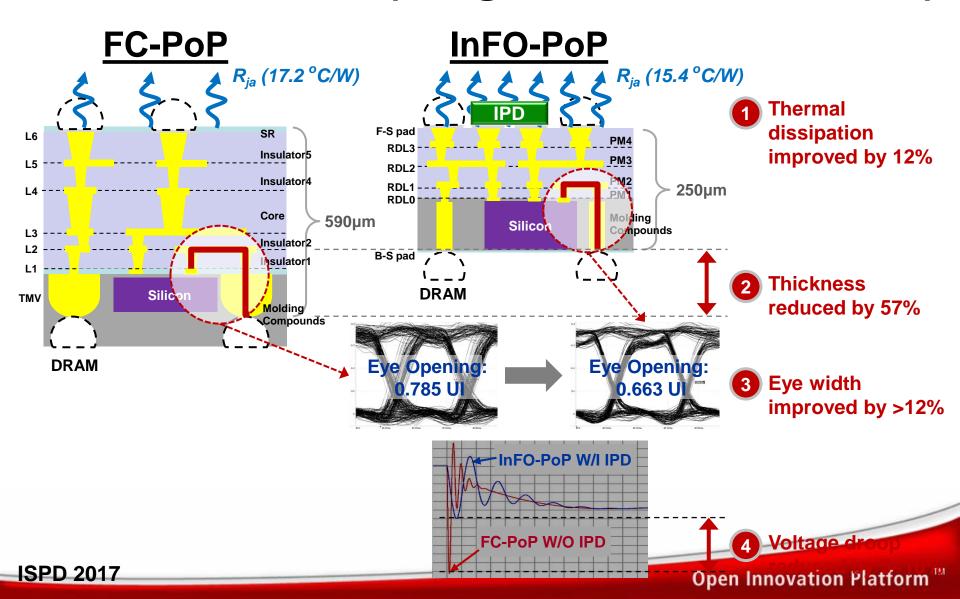

### Advanced Packaging Co-Design – SoC + InFO + IPD (Integrated Passive Device)

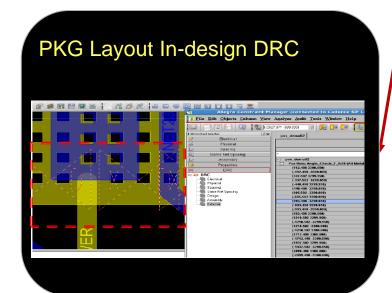

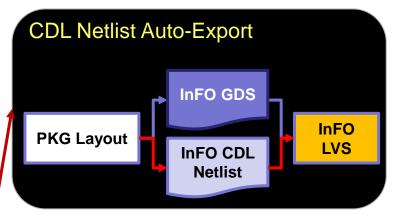

## InFO Design Solutions (InFO Only)

InFO Layout Creation

InFO DRC/LVS

InFO RC Extraction

**RLCK Extraction**

< 4GHz RC/RLCK Extraction for STA, IR, SEM, & PI Analysis

S-parameter Extraction 4GHz – 10GHz S-parameters Extraction for SI/PI, & EMI analysis

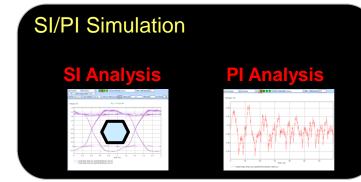

### InFO Design Solutions (Dies + InFO)

SI/PI Simulation Thermal Analysis

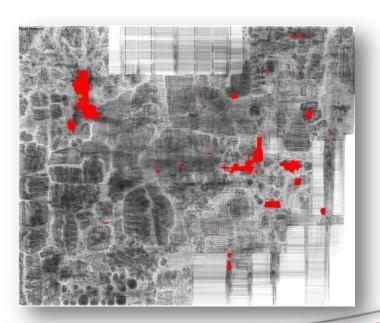

# Applying Machine Learning to Complex Physical Design Problems

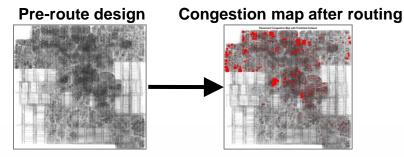

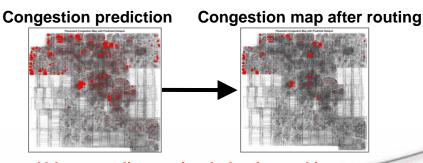

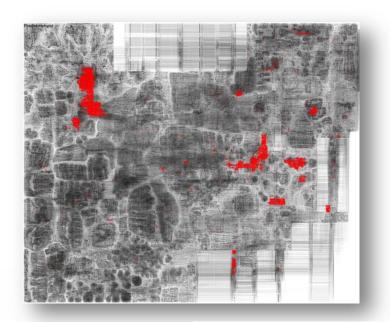

- Place and route Machine Learning experiment

- Feature extraction and convolutional neural network data mapping

- Clock gating and routing congestion speed improvement

## Machine Learning-Based Design Solution

Eliminate human & fixed-model subjective bias with statistical important features

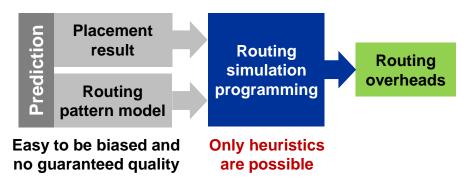

**Traditional EDA Approach**

#### Traditional (EDA) flow

Only know routing results after running routing

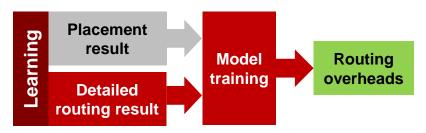

#### **Machine Learning Approach**

Leverage widely used deep learning packages

#### Flow enables by Machine Learning

Able to predict routing behavior and improve congestion with new recipes to achieve 400000

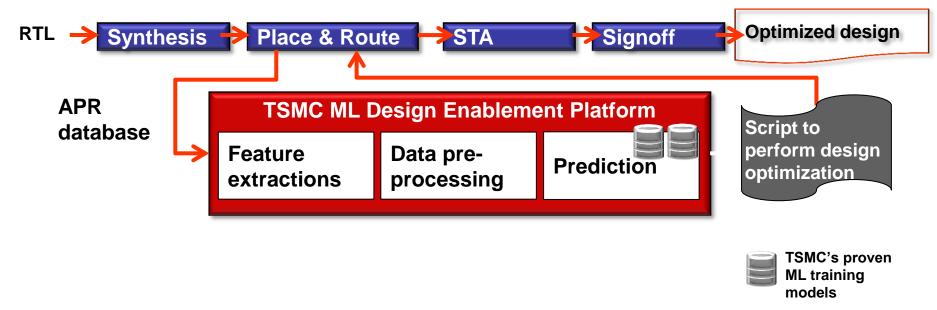

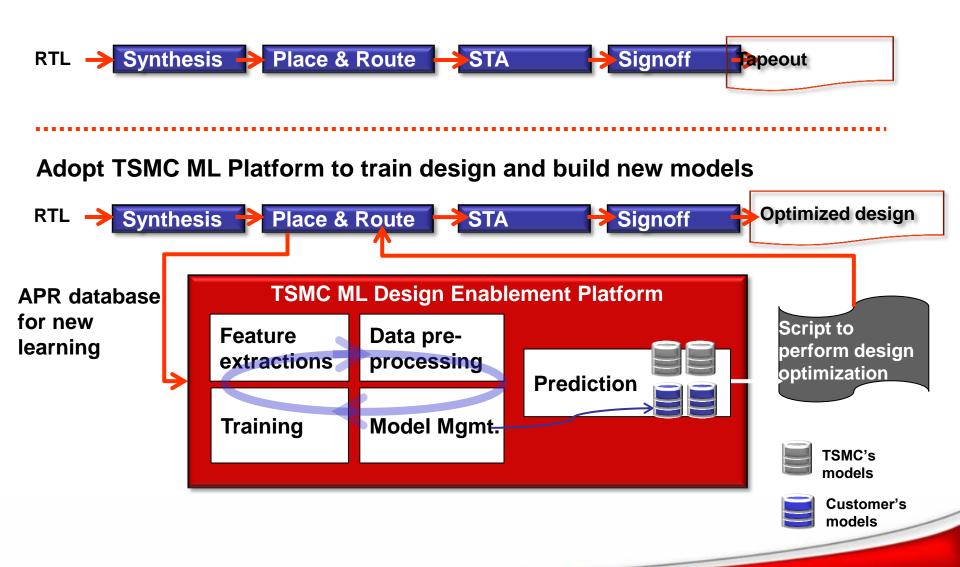

#### **ML Design Enablement Platform**

Adopt TSMC ML Platform to predict the design improvement opportunity

#### **ML Design Enablement Platform**

#### **Performance Gains Prediction from ML**

- Capability to predict and set accurate ARM A72 clock gating latency to avoid over-design and achieve better speed from 50 to 150Mhz

- Post-route speed is improved by 40MHz with detour prediction and early fix

#### Conclusion

- Five semiconductor industry trends, issues and solutions are discussed: area, performance and power scaling, heterogeneous 3D integration and Machine Learning

- Physical design and EDA play even more critical roles to extend Moore's law and to enable highly integrated complex 3D SOC chips