# Silicon Compilers - Version 2.0

# Andreas Olofsson Program Manager, DARPA/MTO

International Symposium on Physical Design March 25-28, Monterey, CA

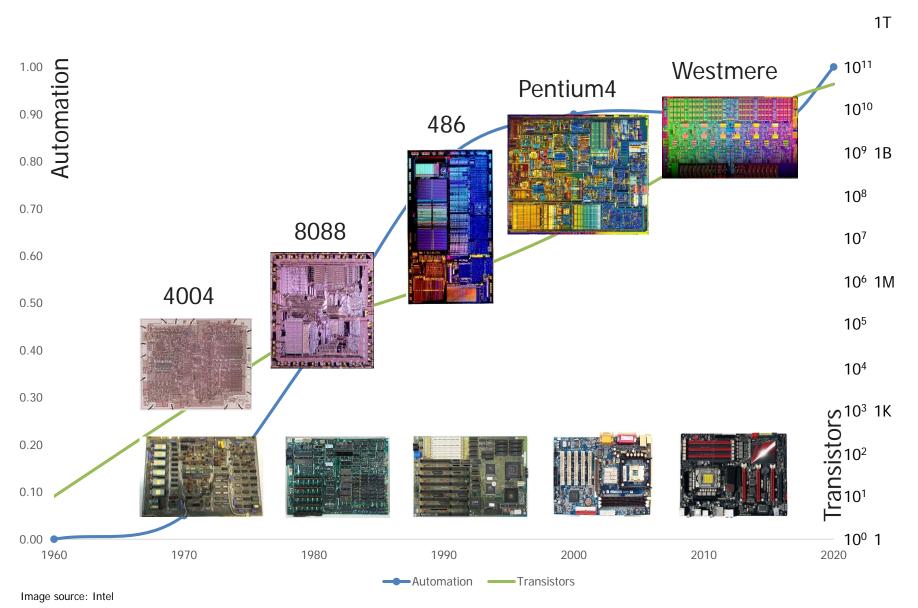

# A Brief History of EDA

### **ENIAC**: A world without Moore's Law

Source: https://en.wikipedia.org/wiki/ENIAC

- First all electric computer

- 357 mults/sec

- \$6.7M (adjusted)

- 20,000 vacuum tubes

- 27 tons

- 5M solder joints!

- 50% uptime

- 2 week compilations

# **DARPA** The modern miracle of Moore's Law

https://www.allpar.com/history

https://www.caranddriver.com/chevrolet/cruze

https://en.wikipedia.org/wiki/ENIAC

https://en.wikipedia.org/wiki/Titan\_(supercomputer)

|                     | 1946 | Today |

|---------------------|------|-------|

| Speed, mph (S)      | 78   | 102   |

| Efficiency, mpg (E) | 14.6 | 22    |

| Cost, \$K (C)       | 1.7  | 27    |

| (S * E ) / C        | 669  | 83    |

|                  | 1946  | Today   |

|------------------|-------|---------|

| Speed, OPS/S (S) | 359   | 17.9e15 |

| OPS/W (E)        | 0.002 | 2e9     |

| Cost, \$M (C)    | 6.5   | 97      |

| (S * E ) / C     | 0.11  | 3e23    |

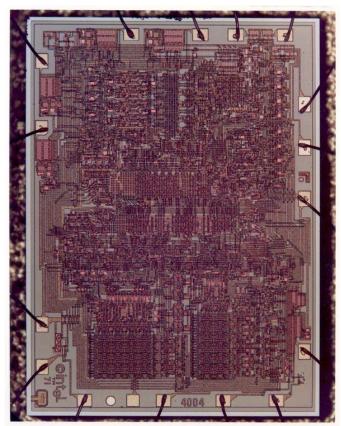

# 1970's: Heroic human efforts

Source: https://en.wikipedia.org/wiki/Intel\_400

- Intel 4004 (1971-1981)

- 10-um feature size

- 2,300 transistors

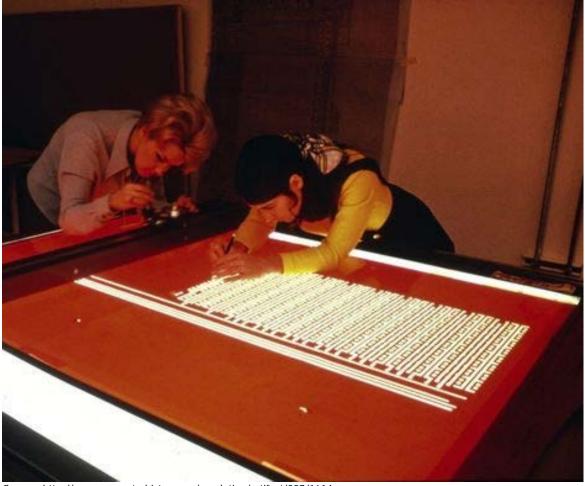

Source: http://www.computerhistory.org/revolution/artifact/287/1614

#### **Rubylith operators**

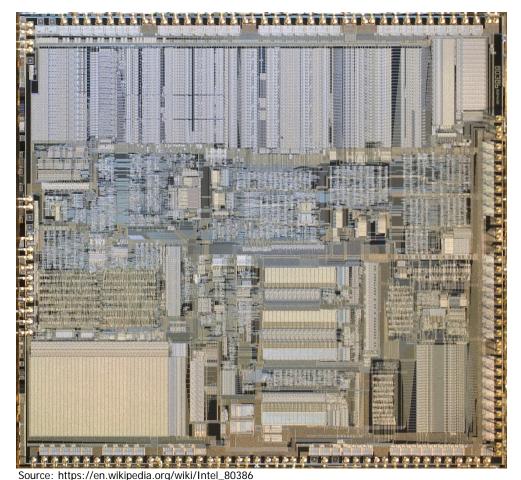

### 1980's: The birth of modern EDA

#### **Synthesis**

Source: https://en.wikipedia.org/wiki/Logic\_synthesis

#### **Layout Systems**

Source: http://opencircuitdesign.com/magic/

#### **Place and Route**

The TimberWolf Placement and Routing Package

Source: http://venividiwiki.ee.virginia.edu/mediawiki/

#### **Framework**

Source: Introduction to VLSI systems by Carver Mead

- Intel 80386 (1985-2007)

- 1-um feature size

- 275,000 transistors

#### **Birth of Modern EDA**

Synopsys

Cadence

Mentor Graphics

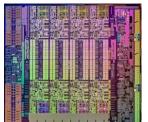

### 1990's-Today: Managing complexity

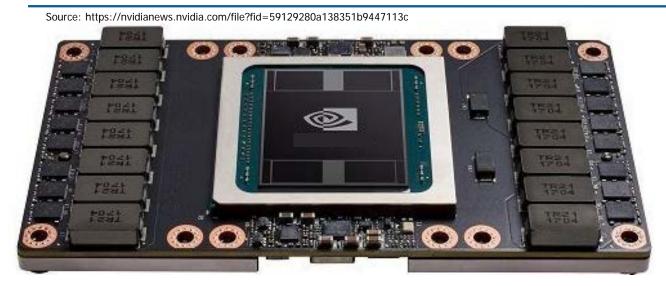

It took several thousand engineers several years to create, at an approximate development cost of \$3 billion. –Jensen Huang

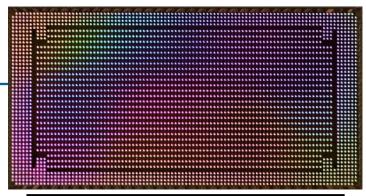

- NVIDIA V100 (2017-)

- 0.012um feature size

- 21,000,000,000 transistors

**Death by a million papercuts...**correctness, application performance, IP integration, power management, firmware, system integration, wire delays, place and route optimization, clocking, packaging, signal integrity, triple patterning, antenna effects, ESD, muti voltage, power gating, multi threshold, area minimization, routing congestion, on-chip variability, self heating, electro migration, SEUs, signal integrity, power delivery networks, decoupling, model accuracy, abstraction layers, low voltage operations, cooling, security, formal proofs, design for test, metal density rules, OPC concerns, timing convergence, yield optimization, static and dynamic power minimization, scan compression, memory BIST, area minimization...

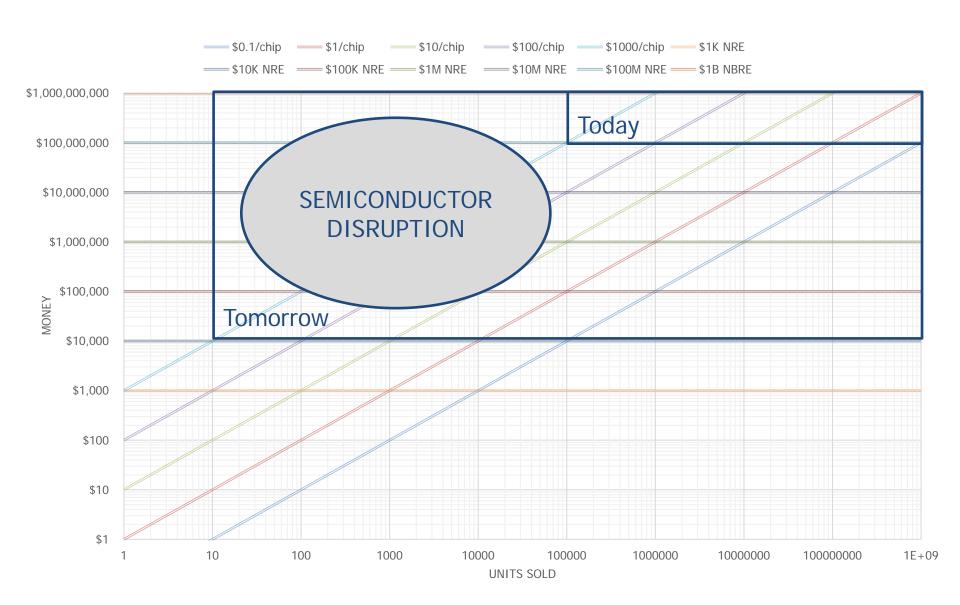

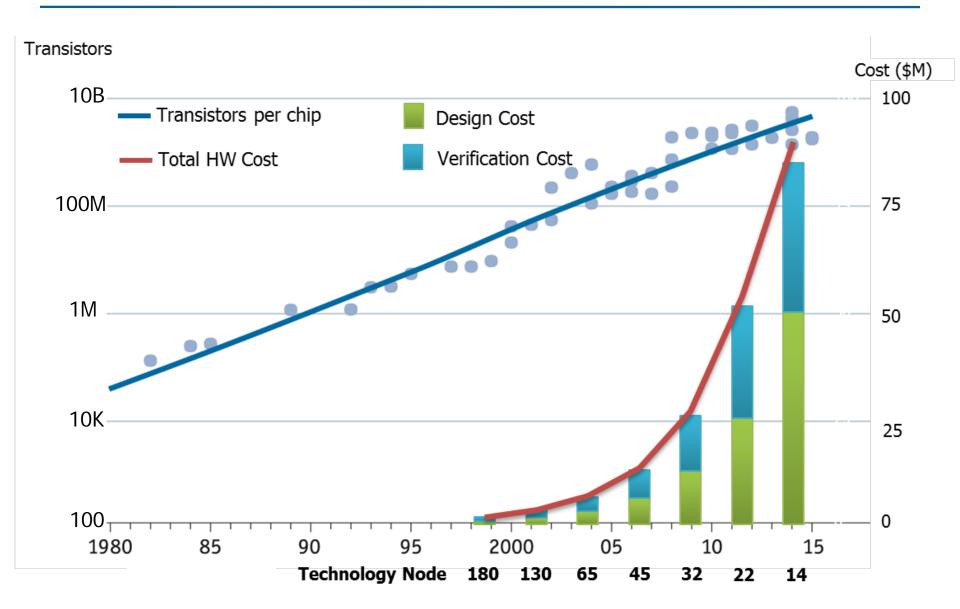

# **DARPA** Has EDA failed to keep up with Moore's Law?

# **DARPA** It's not that simple....

#### "Server Farm":

- One 2010 Dell PowerEdge T610 with a quad-core Xeon 5500 and 32GB DDR3

- One RTL to GDS EDA license

- 12 month design, 24hr spins

| Source:  | Del | ı |

|----------|-----|---|

| Jour CC. |     |   |

| Designer         | Responsibility      | Man-Hours |

|------------------|---------------------|-----------|

| Contractor A     | FPU                 | 200       |

| Contractor B     | Verification        | 200       |

| Contractor C     | <b>EDA Services</b> | 112       |

| Ola Jeppsson     | Simulator/SDK       | 500       |

| Andreas Olofsson | Remainder           | 4,100     |

|                    | Value               |

|--------------------|---------------------|

| Process            | TSMC 16FF+          |

| Transistors        | 4.5B                |

| Die Area           | 117 mm <sup>2</sup> |

| Flip Chip Bumps    | 3,460               |

| I/O Signals        | 1,040               |

| Clock Domains      | 1,152               |

| Voltage Domains    | 2,052               |

| Frequency          | 500Mhz*             |

| 32 Performance     | 2 TFLOPS            |

| 64 bit Performance | 1 TFLOPS            |

| Memory Bandwidth   | 16 TB/sec           |

| NOC Bandwidth      | 0.75 TB/sec         |

| Typical Power      | ~10W                |

| Minimum Power      | 1mW                 |

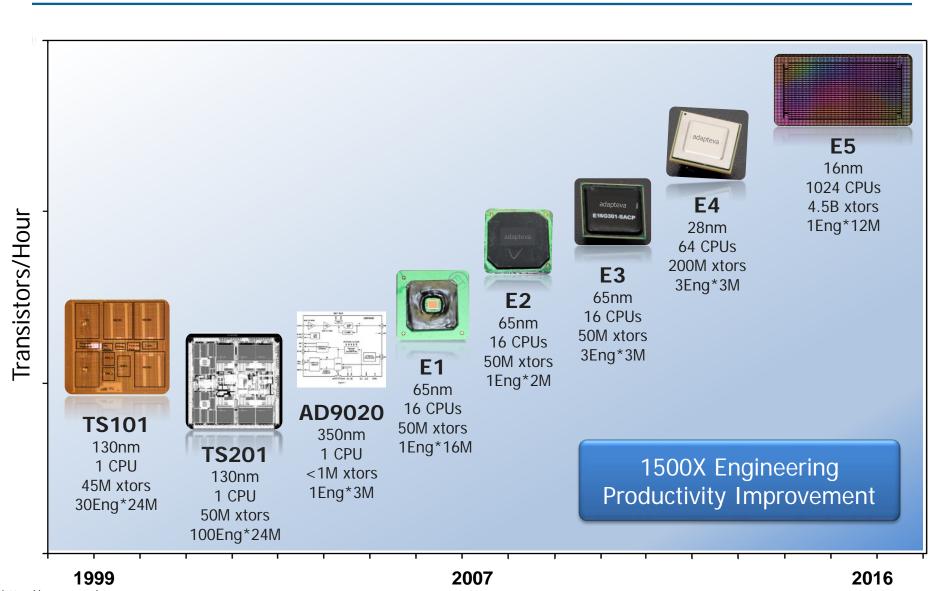

# My personal EDA interaction over 20 years

http://www.analog.com http://www.adapteva.com http://www.ieee.org

### My view: EDA needs to move to 100% automation

### Making the case for democratizing EDA

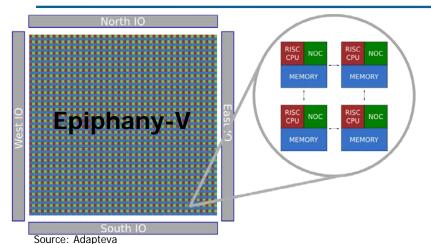

- "Supercomputing for everyone"

- \$99 FPGA + 18 CPU cores @ 5W

- No NDAs!

- Open source and open access

- \$900K raised in 30 days

- First ever crowd funded chip

- 10,000 boards shipped

- 100+ community publications

Open works!

| Metric            | Before | After  | Boost |

|-------------------|--------|--------|-------|

| Customers         | 5      | 10,000 | 2000x |

| Universities      | 1      | 200    | 200x  |

| Site traffic      | 20     | 1,000  | 50x   |

| Twitter Followers | 20     | 6,000  | 50x   |

| Publications      | 2      | 150    | 75X   |

| Govt customers    | 2      | 10     | 5x    |

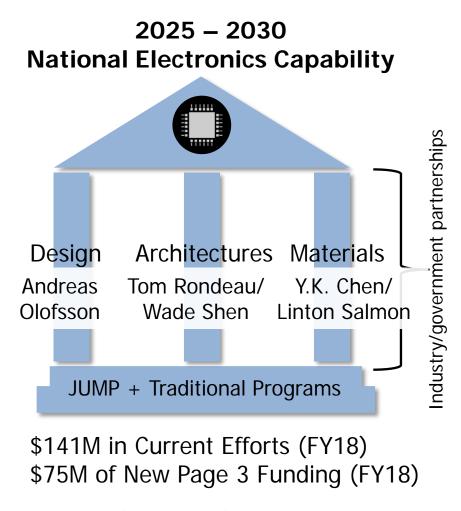

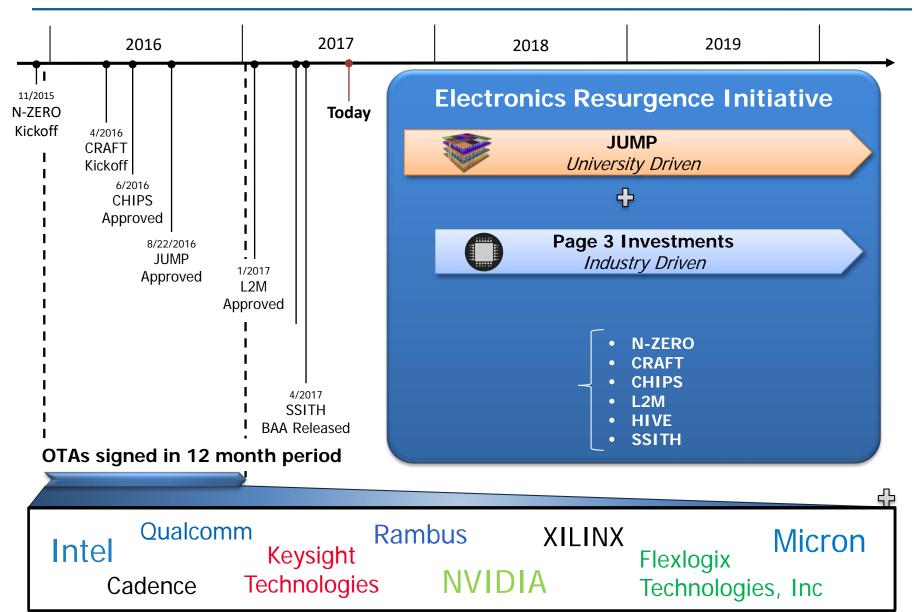

# **Electronic Resurgence Initiative (ERI) Introduction**

### Electronics Resurgence Initiative: Introduction

### Page 3 Investments

#### Design

How do we lower the design barrier to specialization?

#### Architectures

How do we manage the complexity of specialization with new architectures?

#### Materials

How do we integrate new materials for specialized functions?

Resting on a foundation of existing research programs are newly formulated thrusts that all sum into the Electronics Research Initiative, a four-year push with anticipated annual investments in the \$200 million range.

#### Recent DARPA investments and momentum

# ERI "Page 3" Program Service Announcement

#### **Materials & Integration**

- Monolithic Integration of an SoC in Three Dimensions (3DSoC), Linton Salmon

- Framework for Novel Compute (FRANC), Y.K. Chen

#### **Architecture:**

- Software Defined Hardware (SDH), Wade Shen

- Domain-Specific System on Chip (DSSoC), Thomas Rondeau

### Design

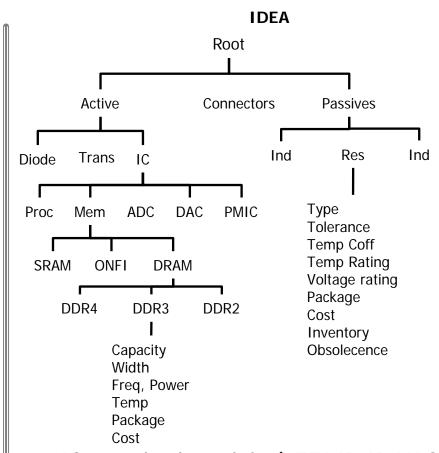

- Intelligent Design of Electronic Assets (IDEA), Andreas Olofsson

- Posh Open Source Hardware (POSH), Andreas Olofsson

# Building a Hardware Compiler at DARPA

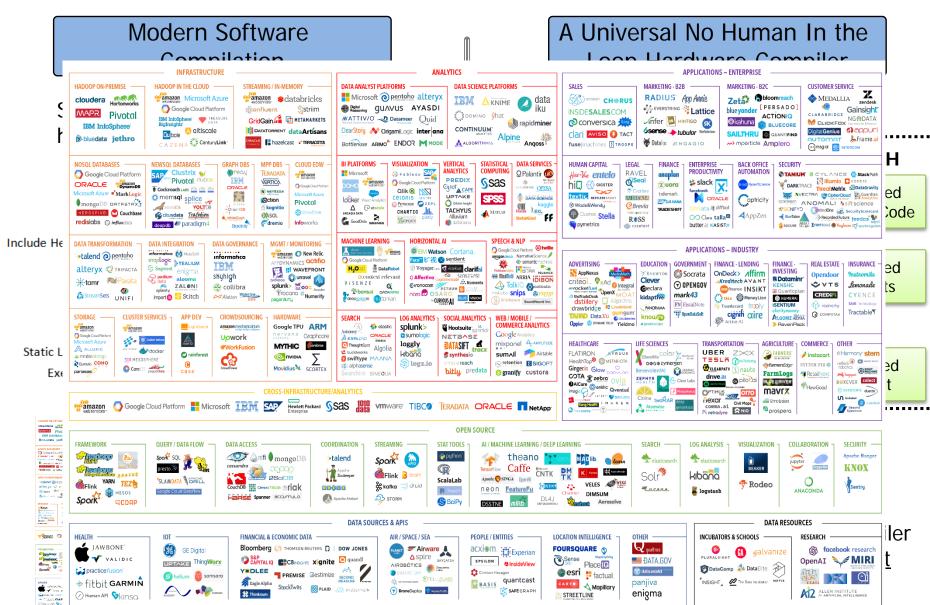

Source: mattturck.com/bigdata2017

# **DARPA** We are building a universal hardware compiler

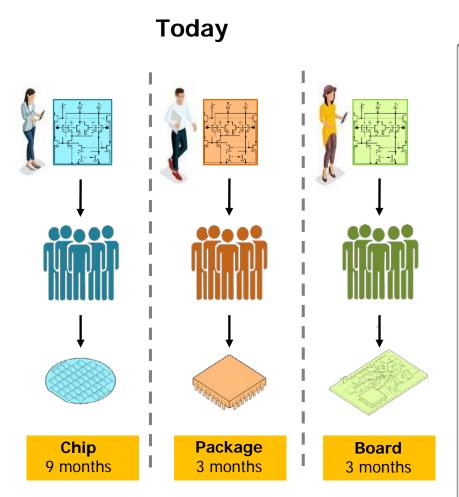

### How is hardware compilation handled today?

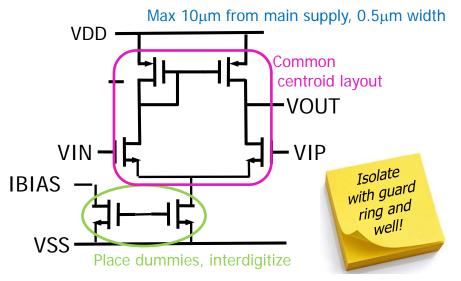

#### **Analog Design:**

- Schematic input

- 1K-100K signals

- 100% EDA assisted manual labor

- 2-4 experts

- 3-18 months

Sources: EETimes

#### **Board Design:**

- Schematic input

- 1-10K signals

- 100% EDA assisted manual labor

- 2-4 experts

- 3-6 months

Digital Design:

- Verilog netlist input, constraints, scripts

- 10M-1B signals

- 99% automated place and route

- 1-100 experts

- 3-18 months

#### Package Design

- Excel spreadsheet input

- 1K signals

- 100% manual labor

- 2-4 experts

- 2-8 weeks

Sources: Intel, NVIDIA, Adapteva

Sources: Axis, Adapteva

### Why now? What has changed?

# Traditional Algorithmic EDA Research

983

#### Optimization by Simulated Annealing

S. Kirkpatrick, C. D. Gelatt, Jr., M. P. Vecchi

with N, so that in practice exact solutions can be attempted only on problems involving a few hundred cities or less. The traveling salesman belongs to the large class of NP-complete (nondeterministic polynomial time complete) problems, which has received extensive study in the past 10 years (3). No method for exact solution with a computing effort bounded by a power of N has been found for any of these problems, but if

An Intelligent Compiler SubSystem for a Silicon Compiler

> David L. Johannsen Steve K. Tsubota Ken McElvain 3/27/87

# How to automate analog IC designs

Knowledge-based systems are relieving the labor-intensive bottlenecks usually associated with such building blocks as op amps and voltage reference.

1993-2018 (stable evolutionary progress)

Optimization algorithms, Productivity & Integration

Cadence Synopsys Mentor Graphics

Ref-2003: The Tides of EDA, Alberto Sangiovanni-Vincentelli

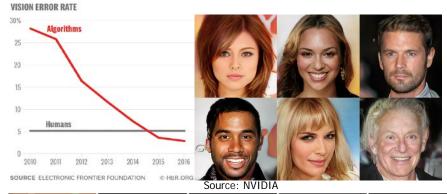

#### A New Machine Learning Based EDA Approach

- ML Algorithm Innovations

- Data driven

- Massive compute (Moore's Law)

- Replacing existing heuristics/humans

monota in the second se

Can we map a layout cost function to ML? Can we access/label enough quality data?

# Why now? (how this approach is different)

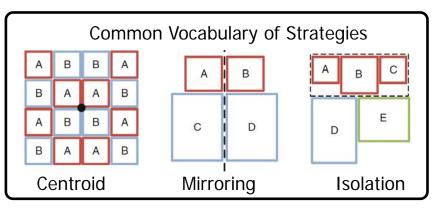

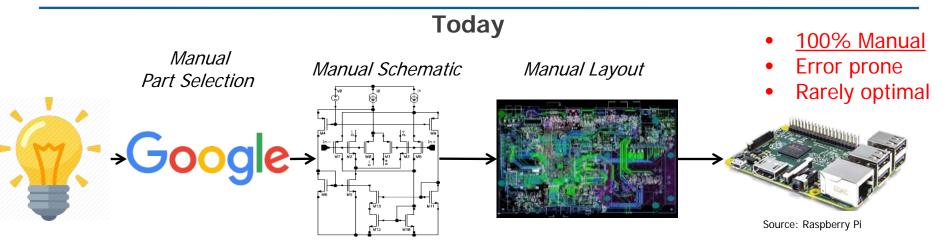

# Today

Designer provides manual constraints to layout person (or EDA tool)

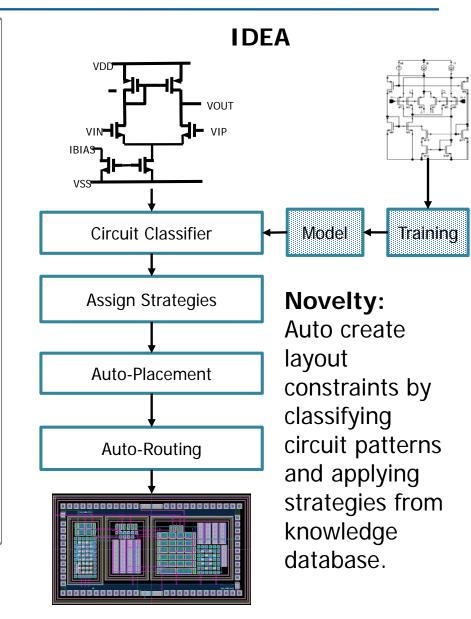

# Intelligent Design of Electronic Assets (IDEA)

### **IDEA Program Objective**

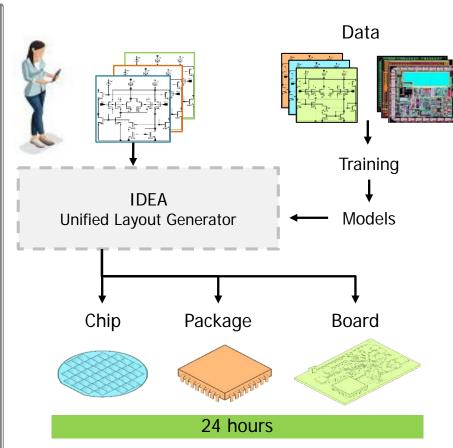

IDEA will create a no-human-in-the-loop hardware compiler for translating source code to layouts of System-On-Chips, System-In-Packages, and Printed Circuit Boards in less than 24 hours

# TA1: A unified electrical circuit layout generator

- Knowledge embedded in humans

- Limited knowledge reuse

- Reliance on scarce resources

**IDEA**

- Knowledge embedded in software

- 100% automation

- 24 hour turnaround

# **Assessing IDEA Difficult Levels**

#### Hard:

- Reinventing board/package design

- Embedding knowledge in digital EDA tools

#### Harder:

- Making an EDA product

- 24 hour turnaround time

#### Hardest:

Robust fully autonomous analog layout

Source: Pearson InformIT

| Technical Area                                        | Metrics                                                                     | Phase 1                                                | Phase 2                                                         |

|-------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------|

|                                                       | SoC Benchmarks                                                              | Government<br>furnished<br>benchmarks<br>14nm CMOS PDK | Government<br>furnished<br>benchmarks<br>7nm & 14nm CMOS<br>PDK |

|                                                       | Board Benchmarks                                                            | BeagleBone Black <sup>1</sup>                          | Open Compute<br>Server <sup>2</sup>                             |

| IDEA TA-1:<br>Machine<br>Generated<br>Physical Layout | SiP Benchmarks                                                              | Government<br>furnished<br>benchmarks                  | Government<br>furnished<br>benchmarks                           |

|                                                       | Benchmark<br>PPA <sub>IDEA</sub> /PPA <sub>Traditional</sub> <sup>(3)</sup> | 0.5                                                    | 1                                                               |

|                                                       | Package Complexity                                                          | Up to 2 die, 2.5D                                      | Up to 1024 die, 2.5D                                            |

|                                                       | Automation                                                                  | 100%                                                   |                                                                 |

|                                                       | Turnaround time                                                             | 24 hours                                               |                                                                 |

|                                                       | Deliverable                                                                 | Software, license <sup>4</sup> , so                    | ftware documentation                                            |

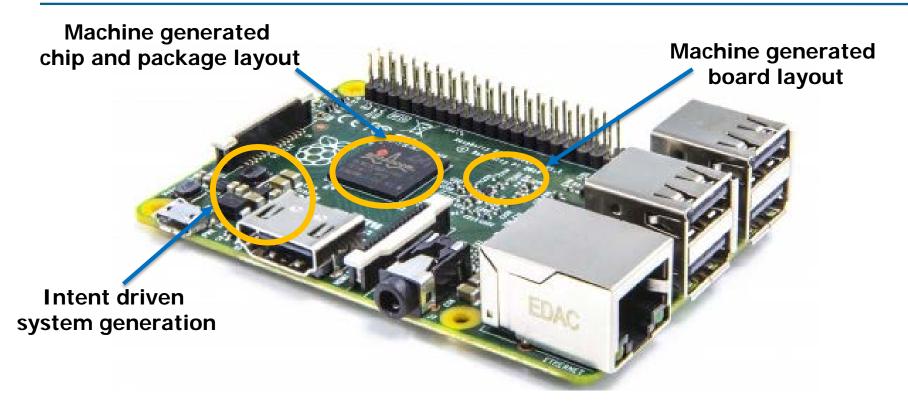

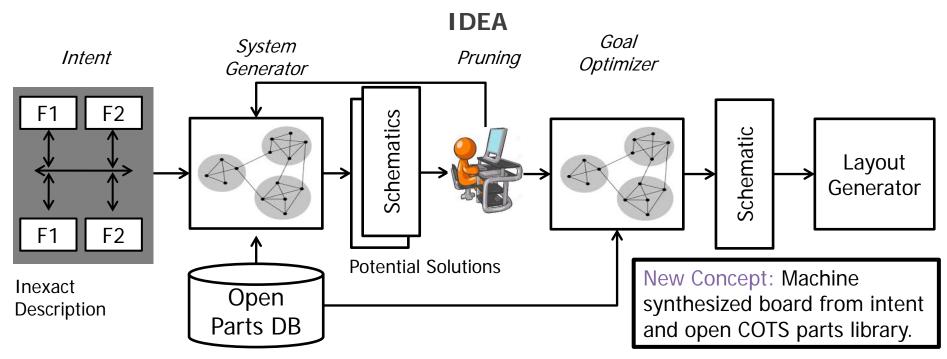

# **DARPA TA2**: Intent Driven Synthesis

True Specs:

5V

Ethernet

USB

HDMI

1GB RAM

128MB Flash

FPGPA

20 GFLOPS

ARM A9

**Intent:** Specify what, not how! Most true board specifications should be very minimal. Derived: 500 Parts, voltage levels, placement, routing, connectivity

# **TA2**: Reinventing Board Development

# **DARPA** TA2: An Open 5M+ Component IC Database

#### **Today**

- 5M+ parts in circulation

- Information embedded in datasheets and reference designs

- No standard models

- Automatic optimization not possible

- IC standard models (LEF,LIB,IP-XACT)

- Extend standards for boards / SIPs

- Creation of 5M+ part DB

- Model all properties needed for constraint based system optimization

| Technical Area                          | Metrics                                                          | Phase 1                                | Phase 2                                                                                         |

|-----------------------------------------|------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------|

|                                         | SoC Benchmark                                                    | SoC with 10 IPs                        | SoC with 100 IPs                                                                                |

|                                         | PCB Benchmark                                                    | BeagleBone Black                       | Open Compute<br>Board                                                                           |

| TA–2: Intent Driven<br>System Synthesis | SiP Benchmark                                                    | Establish pathway<br>to SiP generation | Demonstrated<br>fully automated<br>layout of SiPs<br>with >100<br>chiplets and<br>>100,000 nets |

|                                         | Benchmark<br>PPA <sub>IDEA</sub> /PPA <sub>Traditional</sub> (3) | 0.5                                    | 1                                                                                               |

|                                         | Automation                                                       | 100%                                   |                                                                                                 |

|                                         | Turn around time                                                 | 24 hours                               |                                                                                                 |

|                                         | Deliverable                                                      | Software, license <sup>4</sup> , c     | documentation                                                                                   |

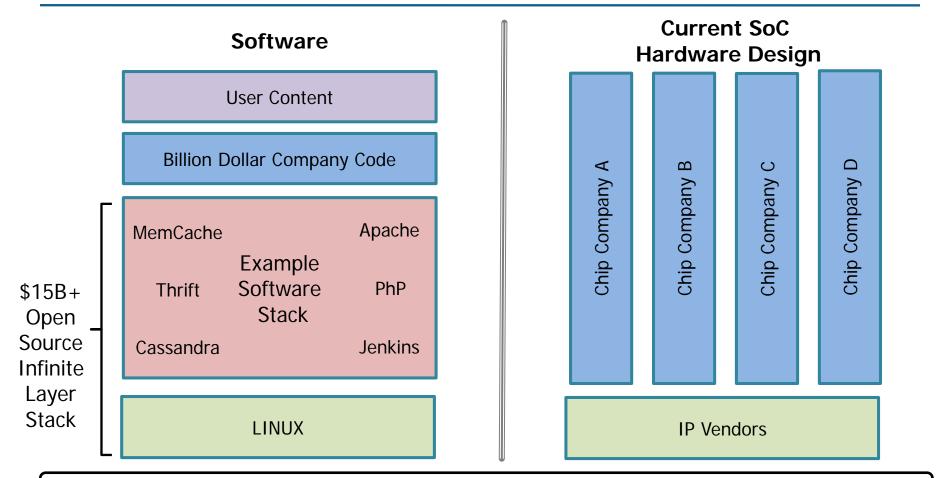

# Posh Open Source Hardware (POSH)

### Reinventing the Hardware IP Stack

POSH will create a viable open source hardware design and verification ecosystem that enables cost effective design of ultra-complex SoCs.

### How is Hardware Different from Software?

|              | Software | Hardware        |

|--------------|----------|-----------------|

| Programmers  | Millions | Thousands       |

| Writing Code | Easy     | Hard            |

| Reading Code | Hard     | Very hard       |

| Debugging    | Hard     | Near impossible |

| Cost of bugs | Low      | Very high       |

What technologies are needed to make open source hardware viable?

## The State of Open Source Hardware

Open Cores

**GitHub**

RISC-V

Open Compute Project

FOSSi Foundation

Still a long way to go!

# POSH Program Structure

TA-1: Hardware Assurance Technology: Development of hardware assurance technology appropriate for signoff quality validation of deeply hierarchical analog and digital circuits of unknown origin.

•

TA-2: Open Source Hardware Technology: Development of design methods, standards, and critical IP components needed to kick-start a viable open source SoC eco-system.

•

TA-3: Open Source System-On-Chip Demonstration: Demonstration of open source hardware viability through the design of a state of the art open source System-On-Chip.

## **TA1:** Hardware Assurance Technology

| Level | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| L3    | Accessible open API hardware emulation and prototyping platforms                      |

| L2    | Scalable open API mixed accuracy simulation tools                                     |

| L1    | Formal tools for assessing relative and absolute quality of hardware library modules. |

Increasing levels of assurance

L3: Emulation & Prototypes

L2: Simulation

L1: Formal Analysis

### **TA1:** Hardware Example Metrics

- "Zero" engineering effort formal proofs of security, power, functionality properties for 1 billion transistor designs.

- 1MHz cycle-accurate simulation speed of a 1 billion transistor design.

- Demonstration of open source framework that automatically partitions large system simulations across hardware emulation, prototyping, cycle accurate simulation, and QEMU style software emulation resources.

# **TA2:** Open Source Technology

| Digital Circuit IP Blocks                     |

|-----------------------------------------------|

| FPGA Fabric                                   |

| Multi-core 64-bit RISC-V processor sub-system |

| GPU (OpenGL ES 3.0)                           |

| PCI Express Controller                        |

| Ethernet Controller                           |

| Memory Controllers                            |

| USB 3.0 Controller                            |

| MIPI Camera Serial Interface controller       |

| CPU Subsystem                                 |

| H264 encoder/decoder                          |

| AES256 encrypt/decrypt                        |

| SHA-2/SHA-3 accelerator                       |

| Secure Digital Controller                     |

| High Definition Multimedia Interface          |

| Serial ATA Controller                         |

| JESD204B Controller                           |

| NAND Flash Controller                         |

| CAN Controller                                |

| Mixed Signal<br>Circuit IP Blocks | Description                               |

|-----------------------------------|-------------------------------------------|

| Standard I/O interfaces PHYs      | DDR, PCIe, SATA, USB,<br>XAUI, CPRI       |

| PLL                               | Range: 10MHz – 10GHz                      |

| DLL                               | Range: 10Mhz – 10GHz                      |

| Analog to Digital<br>Converters   | Range: 1 – 10,000 MSPS                    |

| Digital to Analog<br>Converters   | Range: 1 – 10,000 MSPS                    |

| Voltage Regulators                | Input: 1.8V – 12V, Output<br>0.25V – 1.8V |

| Monitor circuits                  | Temperature, voltage, process             |

How can we cost effectively develop and maintain a high quality catalog of portable open source digital and analog components?

# Conclusion

# IDEA/POSH End State – A Universal Hardware Compiler

```

$ git clone https://github.com/darpa/idea

$ git clone https://github.com/darpa/posh

$ cd posh

$ make soc42

```

# **DARPA** IDEA/POSH Societal Implications